good day!

good day!

Hi Matt! Welcome aboard!

Hi Matt! Welcome aboard!

RPG map ?

RPG map ?

if you are 5nm tall, yes!

if you are 5nm tall, yes!

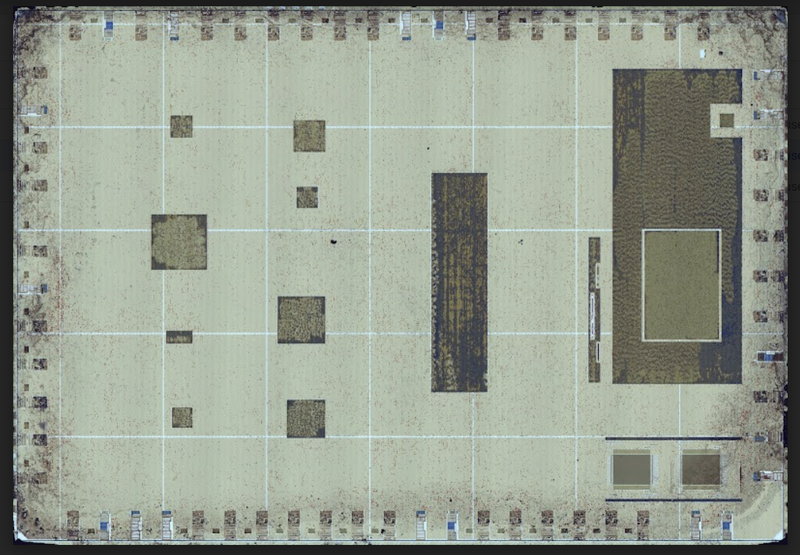

![]() This looks like his MPW1 layout

This looks like his MPW1 layout

yup

yup

It's the new zombie map in Call of Duty

It's the new zombie map in Call of Duty

yeah it's got that ragged look

yeah it's got that ragged look

this is with top metal removed, which isn't a perfect process

this is with top metal removed, which isn't a perfect process

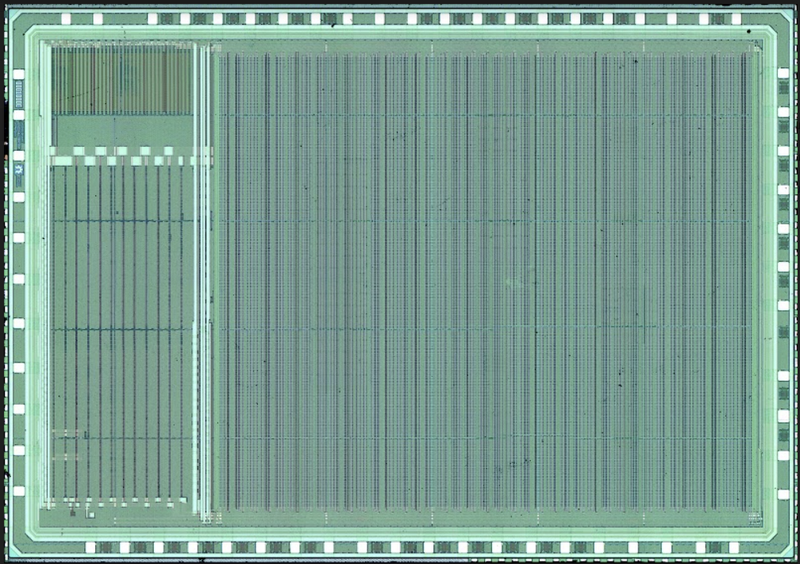

otherwise it looks like this

otherwise it looks like this

spreadsheet mode

spreadsheet mode

Welcome one and all, let's get started! I'm Dan, I'll be modding today with Dusan as we welcome Matt Venn to the Hack Chat to talk about open-source ASICs and spinning up your own silicon.

Welcome one and all, let's get started! I'm Dan, I'll be modding today with Dusan as we welcome Matt Venn to the Hack Chat to talk about open-source ASICs and spinning up your own silicon.

Hi Matt! I know you've been around HaD quite a bit, but care to tell us a bit more about yourself?

Funny that they look so different

Funny that they look so different

hi everyone

hi everyone

hi

hi

yes I've been doing electronics for a long time

yes I've been doing electronics for a long time

when I was a kid I bought maplin kits and assembled them, but didn't know how they worked

when I was a kid I bought maplin kits and assembled them, but didn't know how they worked

I built a door lock that used some recycled 7 seg displays, and I hard wired them to spell 'open' when on, and nothing when off

had no idea about how you would actually count numbers or change text!

had no idea about how you would actually count numbers or change text!

learnt slowly, got into microcontrollers, then fpgas

learnt slowly, got into microcontrollers, then fpgas

got involved with yosyshq and the formal verification tools

got involved with yosyshq and the formal verification tools

open source fpga toolchains

open source fpga toolchains

i was at week of open source hardware (WOSH)

i was at week of open source hardware (WOSH)

when I saw Tim EDwards from Efabless showing a chip made with open source tools

so I downloaded them and tried them on an fpga design (the vga clock)

so I downloaded them and tried them on an fpga design (the vga clock)

I looked at running a course so I could tape-out, but the cost was about 10k,

I looked at running a course so I could tape-out, but the cost was about 10k,

so I canned it. then 6 months later Tim Ansell announced the free shuttle program

so I canned it. then 6 months later Tim Ansell announced the free shuttle program

so I was in a good place and time to jump on and ride the wave

so I was in a good place and time to jump on and ride the wave

now I have 4 tapeouts and preparing for my 5th

now I have 4 tapeouts and preparing for my 5th

160 people have taken my course and about 40 have taped out

160 people have taken my course and about 40 have taped out

mpw5 tapes out on Monday, so I'm getting things ready for that at the moment

mpw5 tapes out on Monday, so I'm getting things ready for that at the moment

![]() what is the process size?

what is the process size?

130nm, which is a kind of hybrid I think. The gate width of the standard cell library are 150nm

130nm, which is a kind of hybrid I think. The gate width of the standard cell library are 150nm

![]() that would be ~1.2V?

that would be ~1.2V?

1.8v core

1.8v core

![]() Can you talk about what sort of FPGA designs can be easily ported? And what's harder coming from an FPGA?

Can you talk about what sort of FPGA designs can be easily ported? And what's harder coming from an FPGA?

the easiest is pure digital with no hard ip blocks like multiplies or brams

the easiest is pure digital with no hard ip blocks like multiplies or brams

you can synthesise small memories with yosys out of flip flops but they are big and don't scale well

you can synthesise small memories with yosys out of flip flops but they are big and don't scale well

we have openram for some hard sram blocks, 1kb in size

![]() And what if we wanted to multiply - just let it synthesize it?

And what if we wanted to multiply - just let it synthesize it?

you could easly build a multiplier as well, for a dsp block but it would probably be quite big and not as efficient as one you'd get on an ecp5 for example

you could easly build a multiplier as well, for a dsp block but it would probably be quite big and not as efficient as one you'd get on an ecp5 for example

yeah

yeah

try not to divide!

try not to divide!

![]() Right, that's true on FPGAs too

Right, that's true on FPGAs too

![]() Can you give an idea of what sort of timing / frequency can be had?

Can you give an idea of what sort of timing / frequency can be had?

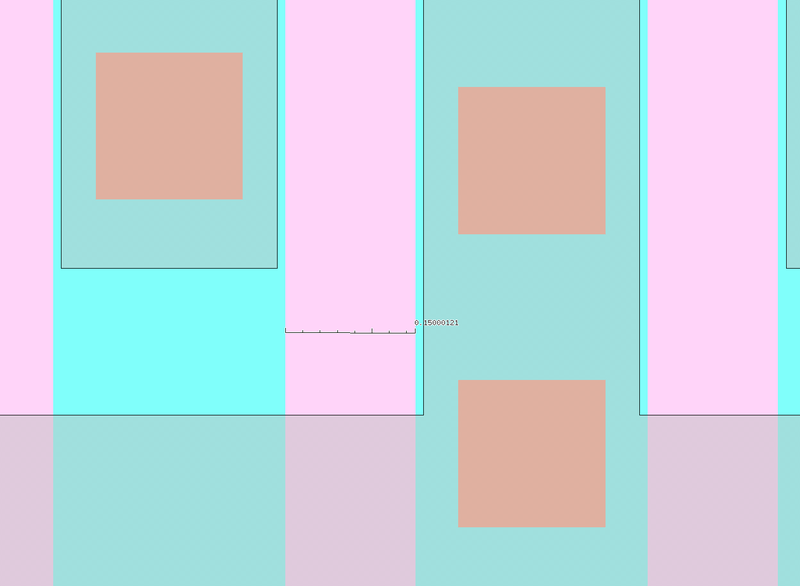

![]() The MPW has 16 slots of 300x300 um areas. Have any of the 160 been too constrained by this for their circuit design?

The MPW has 16 slots of 300x300 um areas. Have any of the 160 been too constrained by this for their circuit design?

so you can do ghz no probs

so you can do ghz no probs

but we have limited bw on the ios, they are quite old and only really go up to 50mhz

but we have limited bw on the ios, they are quite old and only really go up to 50mhz

![]() 300um x 300um or 800um x 800um max size - roughly how many pads and how many gates is realistic?

300um x 300um or 800um x 800um max size - roughly how many pads and how many gates is realistic?

there is an 'analog' version of the submission process that gives you 11 pads with no io pad, so you would have to deal with drive current, esd protection etc yourself, but then you could get ghz in and out of the chip. and it's wlcsp so quite good for high frequency

there is an 'analog' version of the submission process that gives you 11 pads with no io pad, so you would have to deal with drive current, esd protection etc yourself, but then you could get ghz in and out of the chip. and it's wlcsp so quite good for high frequency

![]() How does that work if you only have 50 MHz in - are there PLLs you can design in?

How does that work if you only have 50 MHz in - are there PLLs you can design in?

James, that's actually just what I do for my group submissions

James, that's actually just what I do for my group submissions

so it's a sort of IP/block for the IOs and the design of that is what limits the I/O frequency off the chip?

so it's a sort of IP/block for the IOs and the design of that is what limits the I/O frequency off the chip?

https://www.zerotoasiccourse.com/post/mpw2-submitted/

MPW2 Submitted

We did it! 14 people from the course got their designs into the group submission, and the project was accepted for fabrication. Silicon here we come! You can get all the details on all the projects from the Efabless submission And see how I put the application together here.

Read this on Zero to ASIC Course

the full area is 3000 x 3600 um

the full area is 3000 x 3600 um

there are 40 slots on the free shuttle

there are 40 slots on the free shuttle

I started off applying for 1 each on mpw1 and 2 but from 3 onwards I am putting more on

I started off applying for 1 each on mpw1 and 2 but from 3 onwards I am putting more on

![]() What can you tell us about that frequency counter on there?

What can you tell us about that frequency counter on there?

Ian, yes it's old io inheritted from cypress

Ian, yes it's old io inheritted from cypress

Tom, it's a very simple design I made to teach basic digital design to people who haven't touched digital design before

Tom, it's a very simple design I made to teach basic digital design to people who haven't touched digital design before

edge detecter, counter, 7 seg driver

edge detecter, counter, 7 seg driver

![]() Are each of the designs driven by the PicoRV32 core or are they attached directly to package I/O?

Are each of the designs driven by the PicoRV32 core or are they attached directly to package I/O?

Do you know how things are looking on the analog side for these shuttles now? I started looking at the very start and it was very rough with untrustworthy models. Has this improved?

Do you know how things are looking on the analog side for these shuttles now? I started looking at the very start and it was very rough with untrustworthy models. Has this improved?

https://github.com/mattvenn/frequency_counter

GitHub - mattvenn/frequency_counter

You can't perform that action at this time. You signed in with another tab or window. You signed out in another tab or window. Reload to refresh your session. Reload to refresh your session.

If you only have 50 MHz in - are there PLLs you can design in?

If you only have 50 MHz in - are there PLLs you can design in?

the picorv32 is a coprocessor. it loads the gpio configuratoin and then you can ignore it. but you could add some wishbone peripheral for example and use it to accelerate the pico

the picorv32 is a coprocessor. it loads the gpio configuratoin and then you can ignore it. but you could add some wishbone peripheral for example and use it to accelerate the pico

I usually attach my designs to the output/input pins

I usually attach my designs to the output/input pins

![]() I'm not familiar with wishbone peripherals

I'm not familiar with wishbone peripherals

and to handle multiple designs; on mpw1 I used a big mux (the big rectangle in the first pic I posted), and for mpw2 onwards used tristate outputs

and to handle multiple designs; on mpw1 I used a big mux (the big rectangle in the first pic I posted), and for mpw2 onwards used tristate outputs

itls like 32bit wide spi

itls like 32bit wide spi

Bruce, we have a DLL that can do up to 270 mhz

Bruce, we have a DLL that can do up to 270 mhz

Impressive!

Impressive!

Patrick, analog is getting better. 2 people to watch are Harald Pretl from JKU and Thomas Parry

Patrick, analog is getting better. 2 people to watch are Harald Pretl from JKU and Thomas Parry

wishbone is an open bus standard used for open FPGA IP and apparently in ASICs by now

wishbone is an open bus standard used for open FPGA IP and apparently in ASICs by now

Harald is taping out an audio DAC on MPW5 and Thomas is working on 5ghz satellite transceivers

Harald is taping out an audio DAC on MPW5 and Thomas is working on 5ghz satellite transceivers

you can get to the specs for wishbone from here: https://en.wikipedia.org/wiki/Wishbone_(computer_bus)

you can get to the specs for wishbone from here: https://en.wikipedia.org/wiki/Wishbone_(computer_bus)

If anyone else is lost in the jargon, you can get an explanation here:

If anyone else is lost in the jargon, you can get an explanation here:

https://www.zerotoasiccourse.com/terminology/

Terminology

Learn how to make your own chips!

Read this on Zero to ASIC Course

Thanks for the update @matt venn

Thanks for the update @matt venn

Thanks @Dan Maloney

Thanks @Dan Maloney

I was going to post a link to the projects on efabless website but they have just updated the website and the old links are 404

I was going to post a link to the projects on efabless website but they have just updated the website and the old links are 404

So, just to clarify, the class is not about making chips, but about making ASICs. How does one know what should go on an ASIC and what on a processor? Let's say for example, a sata controller to use with a riscv chip?

So, just to clarify, the class is not about making chips, but about making ASICs. How does one know what should go on an ASIC and what on a processor? Let's say for example, a sata controller to use with a riscv chip?

![]() @Nick Kelsey To get an idea of what density is achievable yosys compiles the picorv32a riscv core to ~15K cells in ~150000um^2, so roughly 400um on a side.

@Nick Kelsey To get an idea of what density is achievable yosys compiles the picorv32a riscv core to ~15K cells in ~150000um^2, so roughly 400um on a side.

Alvaro, I suppose I don't see much difference between an ASIC or an IC. maybe volume? same process in design and manufacture

Alvaro, I suppose I don't see much difference between an ASIC or an IC. maybe volume? same process in design and manufacture

Eric, got any comments on that?

Eric, got any comments on that?

when you say processor, I think CPU, something that goes in your phone or laptop

when you say processor, I think CPU, something that goes in your phone or laptop

that's very general purpose, jack of all trades, master of none

that's very general purpose, jack of all trades, master of none

if you need to accelerate some application, like the sata controller, then you'd design a custom chip for doing that

if you need to accelerate some application, like the sata controller, then you'd design a custom chip for doing that

but you could also use the same tools and process to design a general purpose cpu

but you could also use the same tools and process to design a general purpose cpu

does that help?

does that help?

Yes, thanks. So if I wanted to build a sata chip or a riscv, the course would be a nice help to learn how to do it.

Yes, thanks. So if I wanted to build a sata chip or a riscv, the course would be a nice help to learn how to do it.

Matt, As I recall, back in the early 1990s, it cost a minimum of ~$100K to make an moderately complex ASIC using a fab like VLSI. How has that cost changed today?

Matt, As I recall, back in the early 1990s, it cost a minimum of ~$100K to make an moderately complex ASIC using a fab like VLSI. How has that cost changed today?

Can you talk a little bit about the design tools used for fabrication? With FPGAs there are very simple things to use like ICEStudio where you just draw the fpga design. How easy are the tools to build an ASICs?

Can you talk a little bit about the design tools used for fabrication? With FPGAs there are very simple things to use like ICEStudio where you just draw the fpga design. How easy are the tools to build an ASICs?

Alvaro, yes. I should have said in my intro, that I love science communication as much as I love actually messing around with electronics and hardware design. Now that the barrier to entry is so much lower for this field, I wanted to help people into it. So I am now basically split half science communciation with the course and half engineering with learning how to make chips and get them working.

Alvaro, yes. I should have said in my intro, that I love science communication as much as I love actually messing around with electronics and hardware design. Now that the barrier to entry is so much lower for this field, I wanted to help people into it. So I am now basically split half science communciation with the course and half engineering with learning how to make chips and get them working.

Bruce, I'm not sure how that cost breaks down. But the traditional industry standard (cutting edge) tooling is 100k per seat per year

Bruce, I'm not sure how that cost breaks down. But the traditional industry standard (cutting edge) tooling is 100k per seat per year

the open source tools are no where near the PPA (power performance area) which are common metrics

the open source tools are no where near the PPA (power performance area) which are common metrics

but the actual cost of getting 100 chips made is about 5 to 10k $

but the actual cost of getting 100 chips made is about 5 to 10k $

Joining late, but wanted to throw out that Parallax's P1 has been available for quite some time here https://www.parallax.com/propeller-1/open-source/

Joining late, but wanted to throw out that Parallax's P1 has been available for quite some time here https://www.parallax.com/propeller-1/open-source/

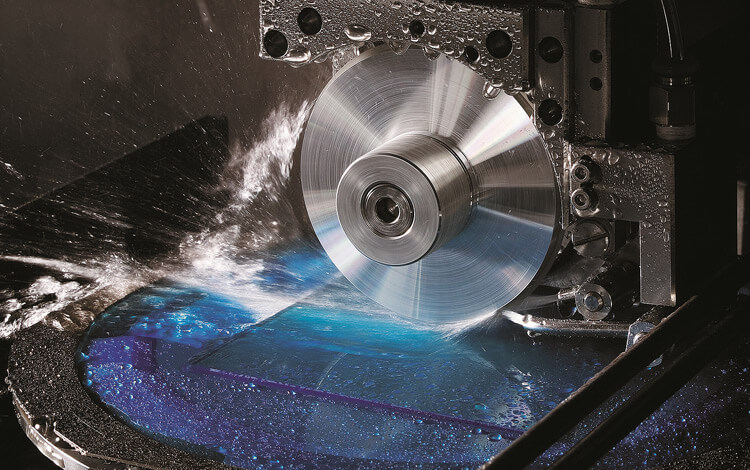

sky130 is about 20 years old, and the mask costs are about 200k $, then maybe 1k per wafer with 4000 chips on t

sky130 is about 20 years old, and the mask costs are about 200k $, then maybe 1k per wafer with 4000 chips on t

so people join together to do an MPW (multi project wafer) run, and split the high NRE cost of the masks between 40 people

so people join together to do an MPW (multi project wafer) run, and split the high NRE cost of the masks between 40 people

![]() how about other interesting cells beyond gates for this process, for example fuse bits, eeprom cells, analog cells, etc

how about other interesting cells beyond gates for this process, for example fuse bits, eeprom cells, analog cells, etc

Matt, back in the 1990s the design tools were always more expensive than cost for prototyping chips! Hasn't changed it seems!

Matt, back in the 1990s the design tools were always more expensive than cost for prototyping chips! Hasn't changed it seems!

Nick, I don't know too much beyond the digital side of things. We have pcells (parametric cells) for analog

Nick, I don't know too much beyond the digital side of things. We have pcells (parametric cells) for analog

so you can size your own transistors, but the analog flow is very manual and hands on compared to the digital flow

so you can size your own transistors, but the analog flow is very manual and hands on compared to the digital flow

sky130b is a variant of sky130a and with a slightly different layer stackup we can have re-ram (resistive ram), but I know nothiing about it

sky130b is a variant of sky130a and with a slightly different layer stackup we can have re-ram (resistive ram), but I know nothiing about it

interesting

interesting

![]() guessing analog is more like laying out a PCB vs digital which is verilog to a layout compiler?

guessing analog is more like laying out a PCB vs digital which is verilog to a layout compiler?

Nick, yeah and you have to size all the transistors yourself and make sure your design simulates to achieve your requirements

Nick, yeah and you have to size all the transistors yourself and make sure your design simulates to achieve your requirements

Thomas Parry did a livestream with me about his process

Thomas Parry did a livestream with me about his process

Dan Maloney

Dan Maloney

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.