Dan Maloney 2:51 PM

Howdy all, welcome to the Hack Chat!

|

Nicolas Tremblay 2:52 PM

Hay Dan! long time no read

|

Dan Maloney 2:53 PM

Indeed, glad to see the old gang again

|

Boian Mitov 2:58 PM

Hello everyone! :-)

|

|

dracolytch 2:58 PM

Good afternoon from DC

|

|

dracolytch 2:59 PM

Raspberry Pi hack chat soon, yes?

|

Richard Hogben 2:59 PM

yep

|

Boian Mitov 2:59 PM

Hope so :-)

|

Dan Maloney 3:00 PM

Yep, starting up in a minute. I don't see Eben logged in yet, might have to wait a few

|

mwsecdev 3:00 PM

Hello all!

|

Dan Maloney 3:01 PM

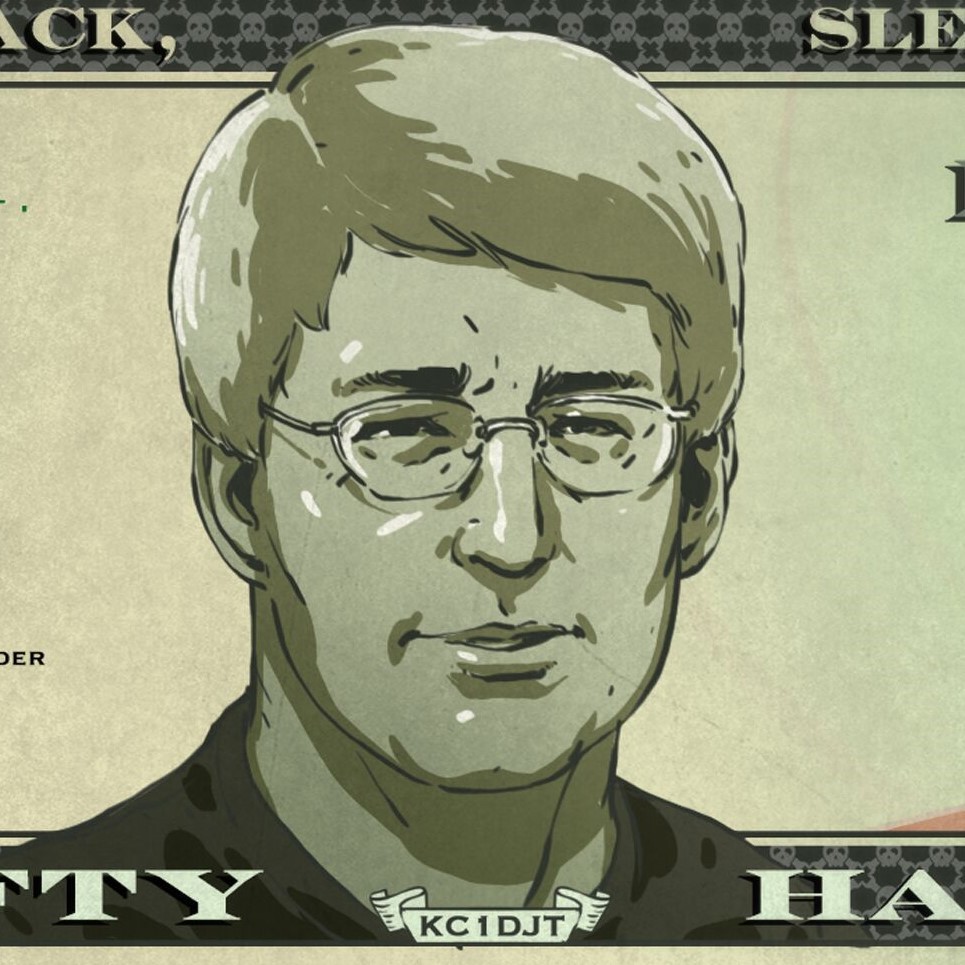

But, let's kick it off while we wait. Welcome to the Hack Chat, I'm Dan and I'll be modding today along with Dusan as we welcome Eben Upton to kick off our 2025 series!

|

|

Chuck.untulis 3:03 PM

Can't hear anything?

|

Dan Maloney 3:04 PM

@Chuck.untulis - it's an all-text chat, no audio. Just waiting for Eben to get online

|

|

Chuck.untulis 3:05 PM

Thanks.

|

Dan Maloney 3:05 PM

Just got word from Eben, he's trying to authenticate. Just a minute now

|

Dan Maloney 3:06 PM

Stupid computers ;-)

|

deʃhipu 3:07 PM

Wait, you mean this is running on a computer? I thought it was just a big anthill in Pasadena.

|

|

fieraangeles 3:07 PM

Hi 👋

|

|

fieraangeles 3:07 PM

What's You name

|

Dan Maloney 3:08 PM

@fieraangeles - Hi, this is Dan and we're doing a Hack Chat today with Eben Upton

|

Dan Maloney 3:09 PM

Just waiting for him to log in -- he said he was in email authentication jail

|

|

eben.upton 3:11 PM

Yay

|

Fred 3:11 PM

Hello Eben!!!

|

curiousmarc 3:11 PM

Howdy

|

|

eben.upton 3:11 PM

Hello

|

|

eben.upton 3:11 PM

Sorry about that. Chrome was sad about the email verif link. Safari was happy.

|

Dan Maloney 3:11 PM

Ah, there we go!

|

Dan Maloney 3:12 PM

Welcome aboard, thanks so much for joining us today!

|

|

eben.upton 3:12 PM

Thank you for having me.

|

Tony White 3:12 PM

woo hoo! Thanks for taking the time!

|

|

eben.upton 3:12 PM

It's been a busy couple of days for us.

|

Dan Maloney 3:13 PM

Normally this is where I say "Tell us a little about yourself", but that seems weird so...

|

|

eben.upton 3:13 PM

"My name is Eben and I used to be an engineer"?

|

deʃhipu 3:14 PM

and then an arrow to the knee?

|

Szaja 3:14 PM

Once engineer, always engineer.

|

Tony White 3:14 PM

I'll kick things off - Do you see standard Raspberry PI models ever gaining the RP2040 microcontroller to manage power, similar to power management hats the community has developed (like this one https://spellfoundry.com/product/sleepy-pi-2/)?

Being able to fully shut off and on the powerful SBC from simple low power microcontroller would be an amazing feature, and enable a lot of applications!

|

|

eben.upton 3:14 PM

The mindset certainly stays with you, even when you mostly interact with the world via email rather than a text editor and C compiler.

|

|

eben.upton 3:15 PM

That's a good question.

|

Boian Mitov 3:15 PM

Hello @eden.upton :-)

|

Boian Mitov 3:15 PM

Hello @eben.upton

|

curiousmarc 3:15 PM

You have been kicked in the office upstairs. That's not always a bad thing.

|

|

eben.upton 3:15 PM

Lots of interesting consequences of the odd order in which we did our ASIC work. (Hi Boian)

|

|

eben.upton 3:16 PM

So RP1 (the IO chip on Pi 5) predates RP2 (RP2040) architecturally.

|

|

Rogan Dawes 3:16 PM

Alternatively, an ultra low power core that can run while the main cores are in deep sleep.

|

|

eben.upton 3:16 PM

And it's only really with RP2 that we got to a uC compute environment we really believe in.

|

|

eben.upton 3:17 PM

So there's a complete M3-based compute subsystem inside RP1, whcih works perfectly well, but which is just sort of "wrong".

|

|

eben.upton 3:18 PM

This has translated into a reluctance to really productionise the fine details of that capability, because the expectation is that if we did an RP1.5 in the future it would actually embed an RP2-series uC.

|

|

eben.upton 3:18 PM

So Phil Elwell's recent work gives you PIO on the pins of a Raspberry Pi 5, but via an abstraction that we are confident we could implement on that RP1.5

|

|

eben.upton 3:19 PM

And I think it's likely that whatever chips we do in the future, of whatever sort, will have an embedded RP2.

|

|

eben.upton 3:19 PM

So to answer the original question yes, I think it's fairly likely we'll grow that capability in a future product. But the timescales are very extended.

|

Nicolas Tremblay 3:20 PM

What are in the works right now, that you can talk about

|

Evan 3:20 PM

Along a similar vein: will Raspberry Pis ever gain the ability to suspend to RAM or have any other low-power modes that would make it more feasible to use RPis in battery-powered devices?

|

Tony White 3:20 PM

Awesome to hear! Good things take time

|

|

eben.upton 3:21 PM

Remember RP1 engineering start was the summer of 2015, and led to a product launch in 2023. Now we've got quicker at doing chips (RP2350 was about two years). But something like an RP1.5, which would be quite complicated compared to a micro is likely a late-2020s thing at the earliest, even if we deprioritised other things.

|

|

eben.upton 3:21 PM

The do indeed.

|

|

eben.upton 3:21 PM

Other things: headered variants of the existing Pico 2 and Pico 2 W (sounds trivial, some devil in the details).

|

Szaja 3:22 PM

I recall that in one of the interviews you mentioned that it would be cool to have low cost BASIC "computer", which could be based on microcontroller. Is that still something you think about?

|

|

eben.upton 3:22 PM

I think we've said we'll look at other network interfaces in the Pico 2 era, having stopped with WiFi/BT on Pico 1. But no specifics yet.

|

|

eben.upton 3:23 PM

Lots more software work on both uC and "big Pi" platforms. There's still more performance to give on Raspberry Pi 5, and that's after posting a ~20% uplift in Geekbench single core and ~50% in multicore since launch.

|

|

eben.upton 3:23 PM

/me checks secret product launch list

|

benbojangles 3:24 PM

Will you release a rpi 3 zero?

I would like small zero form factor sbc with:

- ram options,

- 2 usb-c ports,

- csi camera port,

- gpio,

- wifi 7 with decent mw power,

- pcie micro nvme port

I would like also to have future sbc boards to match Snapdragon XR2 Gen 2 Platform

List of sbcs I own:

-Hummingboard

-Pi2

-Pi zero original

-pi zero w

-pi zero 2w

-orangepi zero 2w

-jetson nano

-Jetson TK1

|

|

eben.upton 3:24 PM

Pi 5 PoE+ HAT+

|

|

rscott2049 3:24 PM

Interesting! I've been working on making RMII work reliably on RP2xxx, and one thing that really made a difference was the DMA sniffer CRC32. Just wish there were two of them so that it wasn't necessary to share between RX/TX...

|

|

eben.upton 3:24 PM

Slightly development hell product that one.

|

|

eben.upton 3:24 PM

So these are really all things we've kind of announced already, but summed up in one place.

|

|

eben.upton 3:25 PM

Re: BASIC computer. I think the Ichigo Jam is this (https://www.hackster.io/news/ichigojam-combines-strawberry-and-raspberry-to-deliver-a-raspberry-pi-pico-powered-educational-micro-66aa5d2f6eec)

|

julian 3:25 PM

Hi, what about nvme on pi 500?

|

keithpenney 3:25 PM

I see RPi moving slowly towards fully open-source silicon, including optional/parallel RISC-V cores on the RP2350, while sort of hedging your bets with the continued presence of Broadcom chips on Pi5 and ARM cores on RP2350. How's the experience been owning your own silicon/cores compared to vendor lock-in? Should we expect the next of the RP2xxx MCUs to be RISC-V only?

|

benbojangles 3:25 PM

i am sat here in chat with the rpi guy while i work on my jetson nano :)

|

Fred 3:25 PM

Pico 0 - just RISC‑V?

|

|

eben.upton 3:25 PM

We were actually aware of the early NXP-based IchigoJam early enough to put some features (notably the stuff at allows DVI-D) into RP2040 in the hope of winning that socket.

|

Tony White 3:26 PM

10BASE-T1S two wire bus support would be really cool!

|

|

eben.upton 3:27 PM

RMII with PIO is fun. We actually have someone scrubbing the existing open source implementation right now.

|

|

eben.upton 3:27 PM

Also hopefully ULPI, so you can hang one (or many!) USB 2.0 PHYs off RP2350

|

Jan Hamal Dvořák 3:28 PM

@eben.upton: Hi! I love teaching kids code on custom RP2040 handheld console, but even more abusing RP2040 digital pins it to receive FM or turn them into delta-sigma ADCs. Will the new RP2350 stepping fix the pads? I would love to use native popcnt instead of emulating it with PIOs. :-)

|

Jan Hamal Dvořák 3:28 PM

ULPI would be incredible!

|

|

eben.upton 3:29 PM

Future zero products. We're aware of the desire for something further up this roadmap. Slightly constrained by our desire to be single-sided (we did the whole RP3A0) development to achieve this, where we could probably have squeezed BCM2837 and discrete LPDDR2 on two sides. I think the 512MB of memory is the largest limiting factor, rather than compute power or interfacing.

|

benbojangles 3:29 PM

so rpi 2w with ram options?

|

|

rscott2049 3:30 PM

You might point them at my repo: https://github.com/rscott2049/pico-rmii-ethernet_nce.git - love to get some help pushing it over the line :-)

|

Josh Pritt 3:30 PM

I have an RPi 500 in my shopping cart at Adafruit waiting to check out but I'm not sure what I'll use it for yet!

|

benbojangles 3:31 PM

and upgrade micro usb to 2xusb-c ports which both offer power or data

|

|

eben.upton 3:31 PM

NVMe on Pi 500. As people have noticed, the PCB has the capability, so we could choose to productionise it. But we were *very* focused on narrowing the spread between the base Pi model and the "hundreds" derivative. That spread is $15 ($55->$70) for Pi 400, but only $10 ($80->$90) for Pi 500, and we throw in an SD card. So NVMe didn't make the cut, and honestly for most users the SD card experience with SDR104 and CQ is very smooth.

|

Fred 3:32 PM

To bad about RPI 5 16GB price point, competion is massive

|

|

eben.upton 3:32 PM

Future "openness" on uC. I think it's very unlikely we'd remove the Arm cores: the ecosystem is just so compelling, and the costs aren't substantial. One thing that's changed since RP2350 launch is that I find it hard to imagine removing Hazard3. Where there was a decent chance that it was a one-product deal before.

|

|

bmonilaws 3:32 PM

I would just like to thank you and team for continuing to work on and improve the Compute Module. The CM4 and now CM5 are really quite amazing, and are the basis of several ideas I am trying to bring to life.

|

Evan 3:33 PM

any word on when the CM5 will get 16GB?

|

|

Steve Markgraf 3:33 PM

I just want to say thank you for adding HSTX to the RP2350, the possibilities together with it are amazing - I'm using it to pump out data collected with the PIO from two external ADCs to a $5 HDMI->USB 3.0 dongle at over 120 MByte/s (https://github.com/steve-m/hsdaoh-rp2350)

|

|

eben.upton 3:34 PM

Nothing to report on pads yet, but we are expecting at least one future stepping to roll up fixes to the various things we found in the Hacking Challenge, so there may be an opportunity there.

|

Dan Maloney 3:35 PM

@Steve Markgraf -- Looks like I have an article to write up this afternoon. Thanks!

|

|

eben.upton 3:35 PM

rpi 2w with ram options: maybe, but RP3A0 is very intricate and stacking a pair of LPDDR2 die in there would be a challenge

|

|

eben.upton 3:35 PM

rscott2049 - will do

|

benbojangles 3:36 PM

what's wrong with single 2gb/4gb chip

|

|

eben.upton 3:37 PM

bmonilaws - thank you for the kind words. CM has been a long journey for us (CM1 came out in 2014, before 1B+), but it feels like it's finally found its feet.

|

benbojangles 3:37 PM

LPDDR4

|

Jan Hamal Dvořák 3:37 PM

@eben.upton: Any chance of future RP2s featuring differential receivers for LVDS and similar?

|

|

eben.upton 3:38 PM

CM5 16GB variants are a thing. I need to check the product brief, but they should be in there now. Buliding next month and in stock in early March.

|

Evan 3:38 PM

thanks

|

Evan 3:39 PM

I'm curious about the single-side constraint on the zeros. I suppose there are probably some users who've built products (cases, etc) that don't provide enough room for chips underneath, but it doesn't have castellated pads like the picos, and if you add headers, the bits sticking out the bottom are going to be taller than most chips anyway. Is it a manufacturing cost/complexity thing?

|

|

eben.upton 3:39 PM

Steve Markgraf - ha, that's awesome. HSTX was a nice idea of Luke's. It just felt so wasteful that many uses of PIO were basically just flat-out data pumps. Absolutely punished the ASIC team getting a duty cycle balanced clock for the double data rate.

|

Paul Beech 星熊 3:39 PM

@eben.upton With TSMC Arizona churning out 4nm chips, any desire to make TSMC Cardiff happen to make RPi silicon in the UK?

|

|

eben.upton 3:41 PM

Differential (or just fast) receivers on future RP2s. With HSTX we do now feel a bit undergunned on the RX side. Perhaps something to look at there in the "next next" uC.

|

|

eben.upton 3:41 PM

I think the single-side constraint on Zero is more in our mind than anything else.

|

|

eben.upton 3:42 PM

And to benbojangles' point, moving away from it would open up the design space quite a bit.

|

benbojangles 3:42 PM

i have used zero sized sbcs with spi chips on the underside

|

|

eben.upton 3:43 PM

We should definitely make TSMC Cardiff (or more properly TSMC Newport) a thing.

|

|

eben.upton 3:43 PM

Or TSMC Sheffield.

|

|

eben.upton 3:43 PM

Wafers are the new spoons.

|

|

eben.upton 3:43 PM

(hi Paul)

|

Paul Beech 星熊 3:43 PM

(Aloha!)

|

|

dratini0 3:44 PM

Are there any plans variant of the CM5 that lacks the RP1 and exposes the second BCM2712 PCIe port instead? I have been thinking of insanity like desoldering the RP1 and replacing it with an interposer to bring out the PCIe lanes on the USB3 or the DSI/CSI pins, but I don't think I have the skills.

|

|

Electronic Eel 3:44 PM

Did you consider adding a high speed usb phy (480MBit/s) to the RP2350? If yes, what was the issue you didn't add it? I find the speed to the host with the existing 12MBit/s usb link quite limiting in comparison to what the pio etc. offer.

|

Evan 3:45 PM

@dratini0 sort of like the old RPi4 pcie hack? https://hackaday.com/2020/07/01/adding-pcie-to-your-raspberry-pi-4-the-easier-way/

|

|

eben.upton 3:45 PM

No plans for an CM5 without RP1. RP1 is very much integral to what a Raspberry Pi is now.

|

|

eben.upton 3:46 PM

We did consider USB 2.0, but the intention is that people can use ULPI for this. It just isn't done yet. Always the philosophy is to give people the core essential features and to make it easy to add the missing stuff for those who want it.

|

|

eben.upton 3:46 PM

USB 1.1 is on there primarily because it's central to the developer experience (MSD, UF2 etc).

|

keithpenney 3:47 PM

How about an RP1 on a standalone PCIe card? An RPi peripheral in my desktop tower...

|

|

eben.upton 3:47 PM

But also to let you build IchigoJam

|

|

dratini0 3:47 PM

@Evan Basically that, yeah. Just BGA and almost impossible to hand-solder.

|

Paul Beech 星熊 3:47 PM

I think the smallest flatware ever hand-crafted in sheffield was only 128nm.

|

|

eben.upton 3:48 PM

keithpenney - ah. Those actually exist, as a byproduct of the development program. No commitment, but I'll add that to the spreadsheet. It is kind of awesome to have a tower PC with full Raspberry Pi I/O.

|

keithpenney 3:48 PM

I'll take two! :)

|

Tom Nardi

Tom Nardi

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.