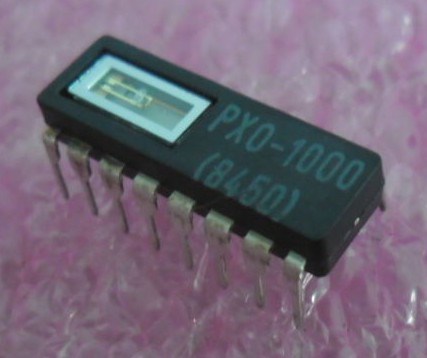

I just discovered this chip : the STATEK PXO-1000 integrated quartz oscillator with integrated predividers.

http://pdf.datasheetarchive.com/datasheetsmain/Datasheets-8/DSA-154595.pdf

Yes it's pretty practical to hack a tiny frequency generator with a minimum part count. I ordered a few of these antiques that don't seem to grow old.

Of course "I could do this with a PIC" but the total absence of programming is worth it :-)

In the same vein, after a hint from @K.C. Lee, I got myself a bunch of PLLs.

Actually it's called a "zero-delay clock buffer" with 8 outputs but the CYPRESS CY2308SC-4 also works as a frequency doubler that can output between 10MHz and 133MHz.

By playing with the feedback signal, not only I can smooth the signal (reducing the jitter) but also bring the frequency much higher. I expect my Rb source to output 20MHz, which will be halved by the ALU, but I can reach up to 120MHz :-)

Another discovery from http://www.jmargolin.com/vgens/vgens.htm :

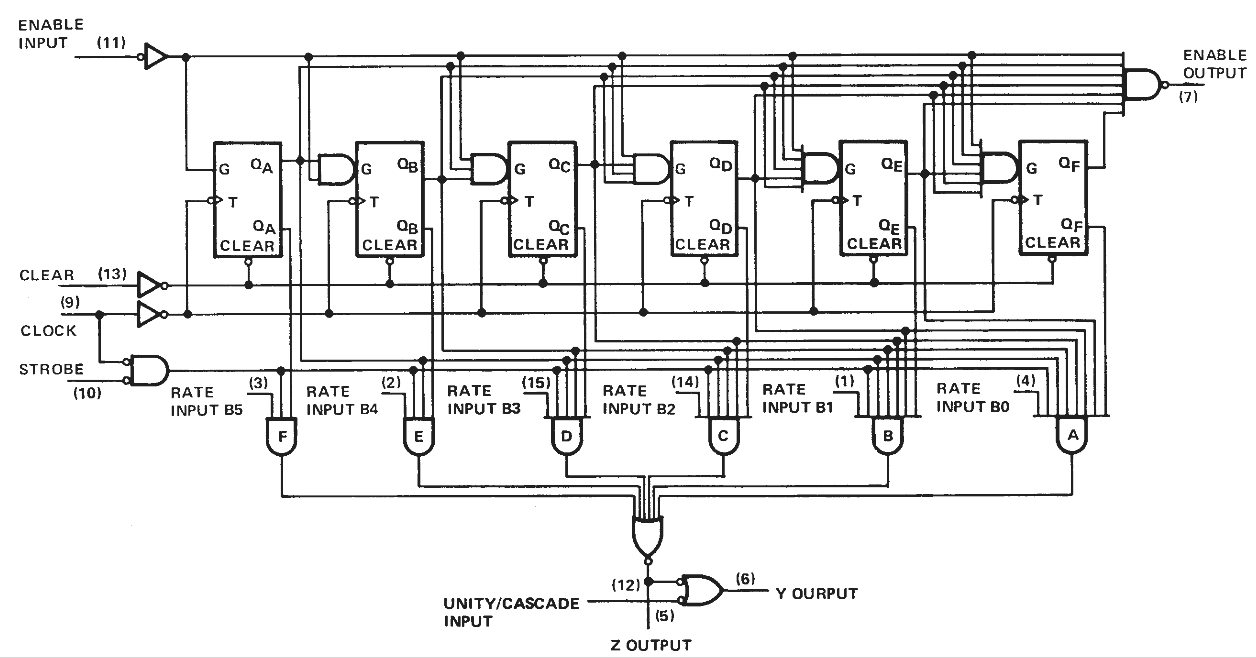

"The BRM used by Atari was the 7497. The 7497 is a 6-bit BRM. With a digital input of 63, it will produce 63 output pulses for every 64 input clocks. With a digital input of 1 it will produce one output pulse every 64 input clocks. Two 7497s were chained together to produce a 12-bit BRM. The data sheet for the 7497 is available here (PDF 282KB)."

Of course, all of this would run faster, better and take less power if I just used a A3P250.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

wow, never seen a chip looking like that.

Are you sure? yes | no

Neither did I.

Instant buy (after consulting online resources).

The DS32KHZ and DS3231 seem to be derived from this hybrid approach, maybe STATEK got bought by Dallas ?

Are you sure? yes | no

You can also add an external divider on the feedback path to do a higher multiplier ratio in a single stage. You can use a loadable counter to implement divide by n.

http://www.cypress.com/file/38066/download figure 13

There are limitations on cascading multiple PLL as it will increase jitters at each stage.

http://www.eetimes.com/document.asp?doc_id=1225577

Are you sure? yes | no

I don't think the CY2308SC has an externally accessible feedback path... Did I overlook something in the datasheet ?

Are you sure? yes | no

16 FBK PLL feedback input

The soic-8 CY2305 has an internal feedback.

Are you sure? yes | no

Daaaaaamn again, you're right... I'll have to examine this. Soon. But now I have to find very high speed predividers...

Are you sure? yes | no

Reading further, I see that the CY2308's REF input is 5V tolerant.

Awesome!

Are you sure? yes | no