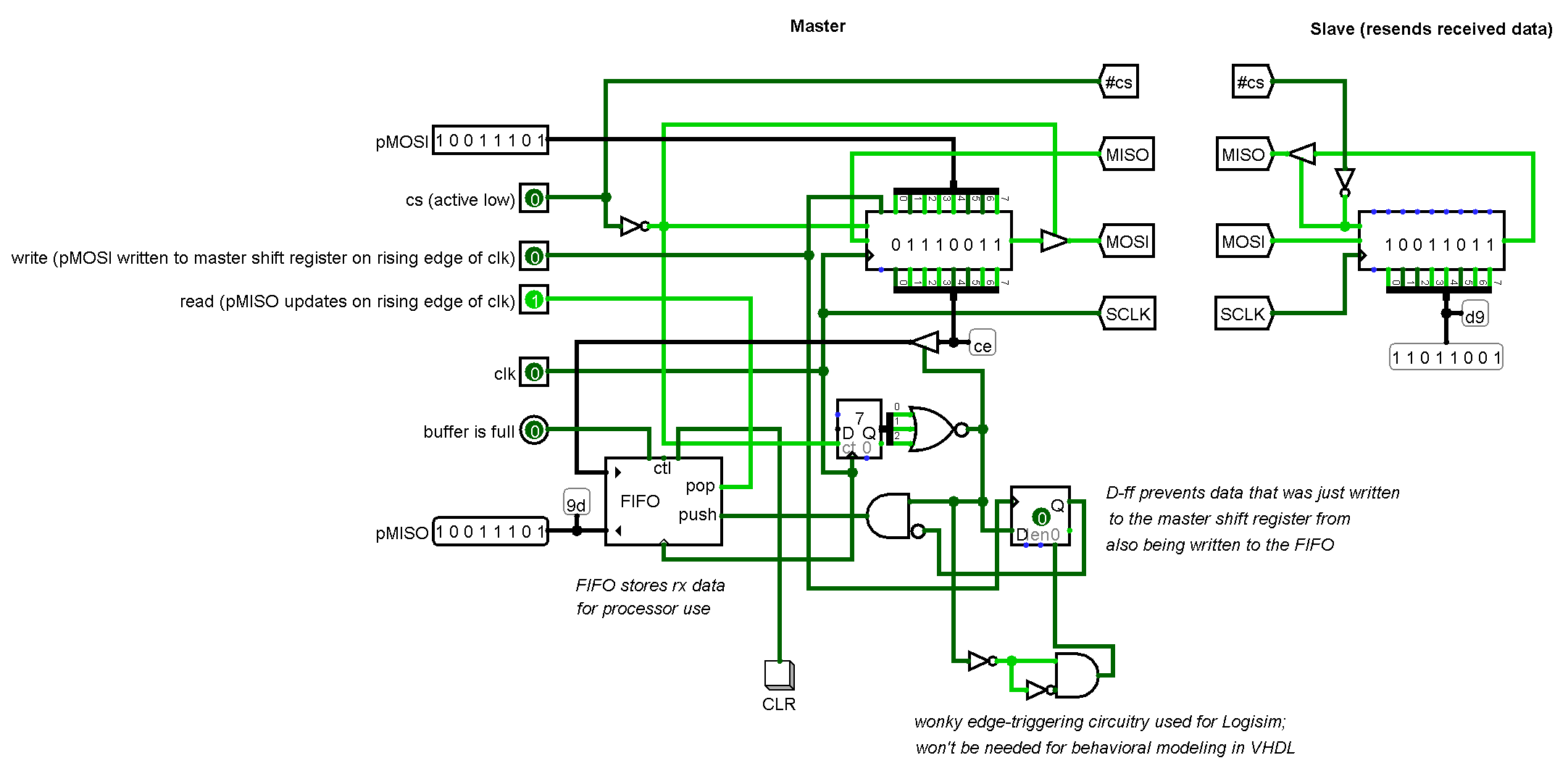

Just finished a design for the SPI controller in Logisim. The slave doesn't really do anything; it shifts out what was shifted in, so when I run the clock for a while, the FIFO fills up with 2 different byte values (master initialized to one value, slave to another). Both the read and write functions are synchronous; the master's shift register only loads from the parallel port when the clock rises and write is high. Similarly, the FIFO only pops the value at the read address when the clock rises and read is high. Currently, with the limited functionality of Logisim block RAM, the FIFO cannot be written to at the same time as it is being read from; this will change for the implementation in VHDL. SPI circuitry below:

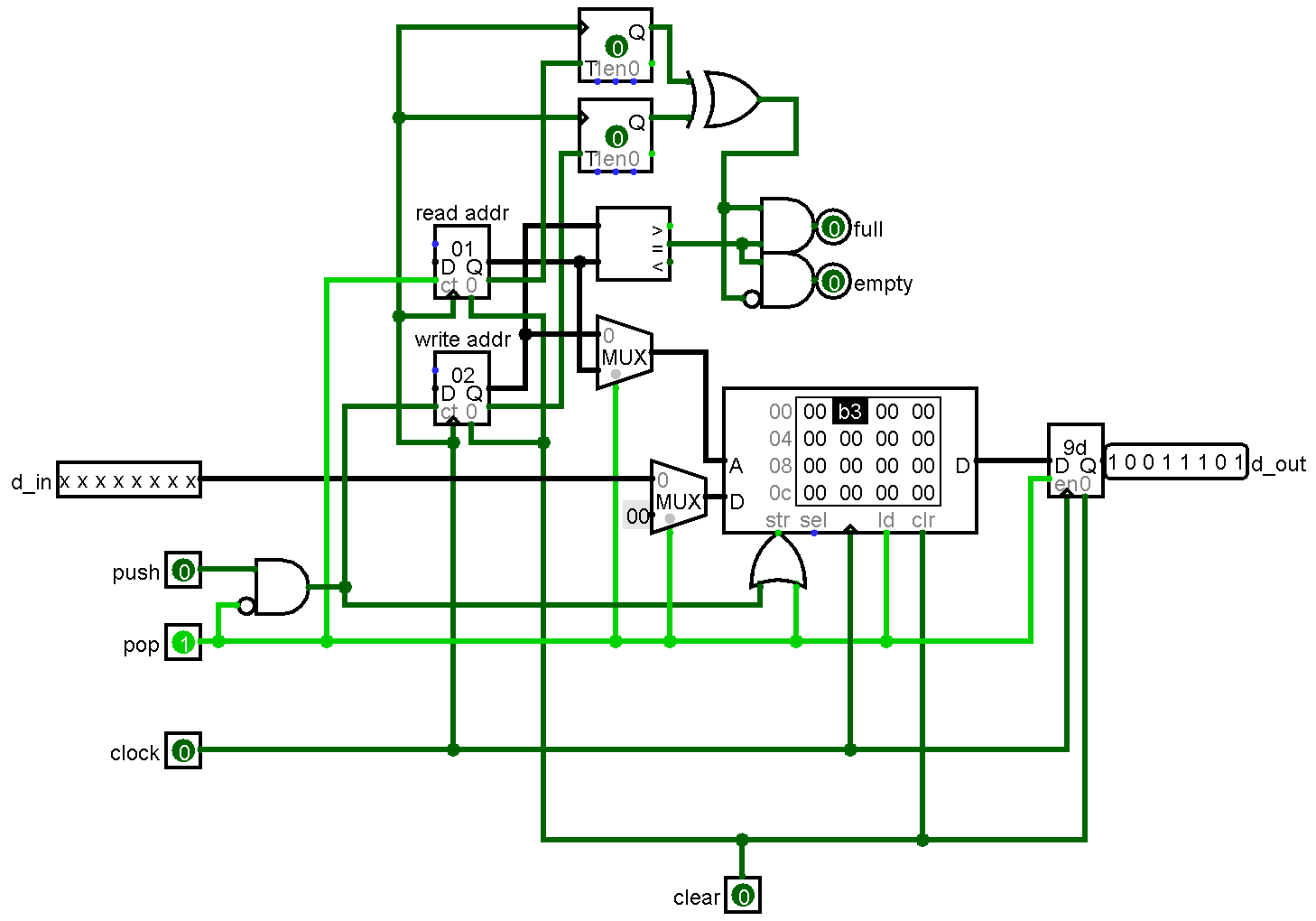

FIFO stack (with less documentation of circuitry):

Reed Foster

Reed Foster

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Hey, this is a great FIFO stack and I wanted to ask you if I can use it in my CPU because I didn't find a MIT license or something like so I wanted to ask you personally, thanks in advance

EDIT: So I found out that I needed a LIFO stack and I made one myself.

Are you sure? yes | no