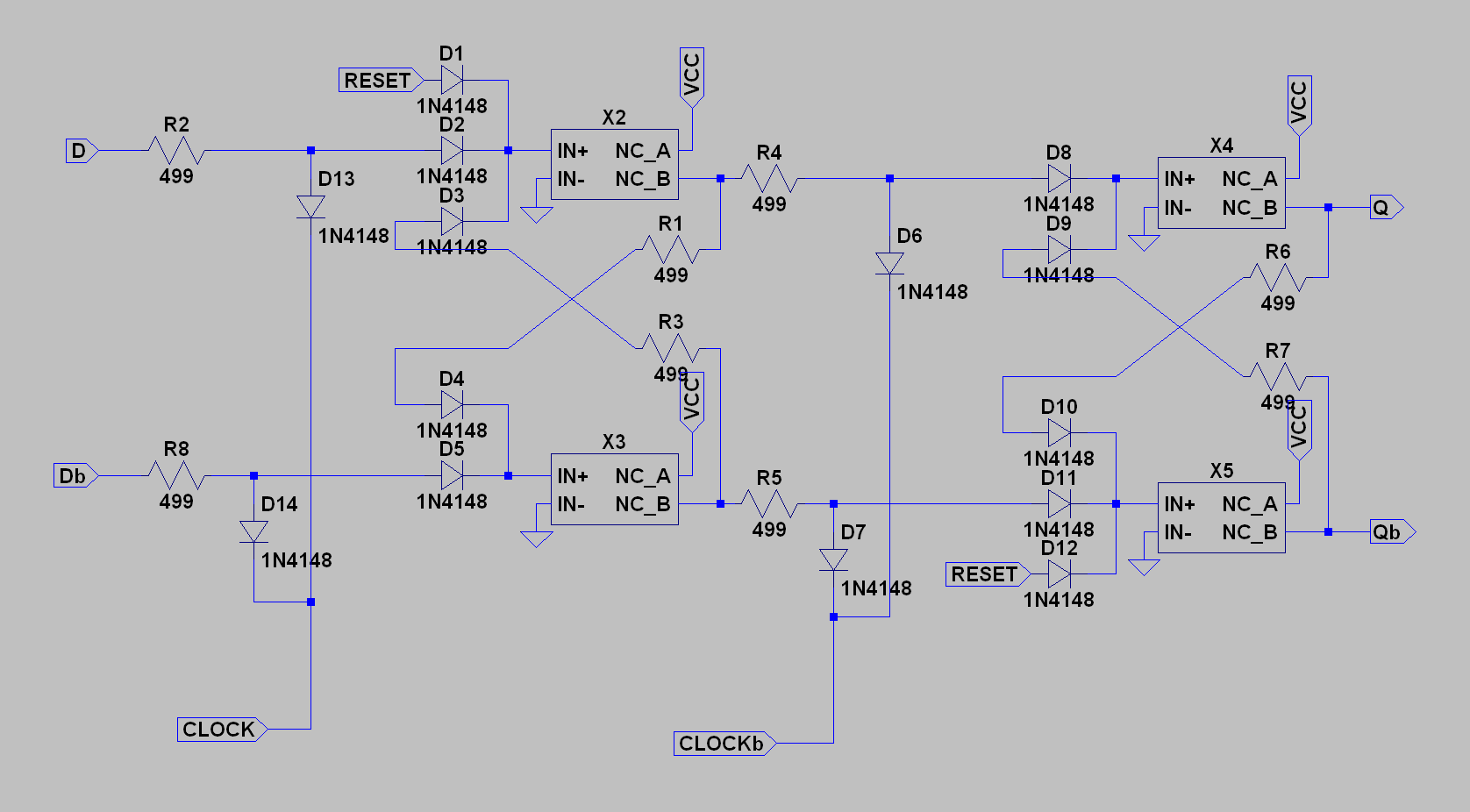

I spent a little time today to get a full simulation of one digit going. The box of relays arrived yesterday, but I had to be elsewhere today, so simulation will have to do for now. The counter is made from D-flip flops like this one:

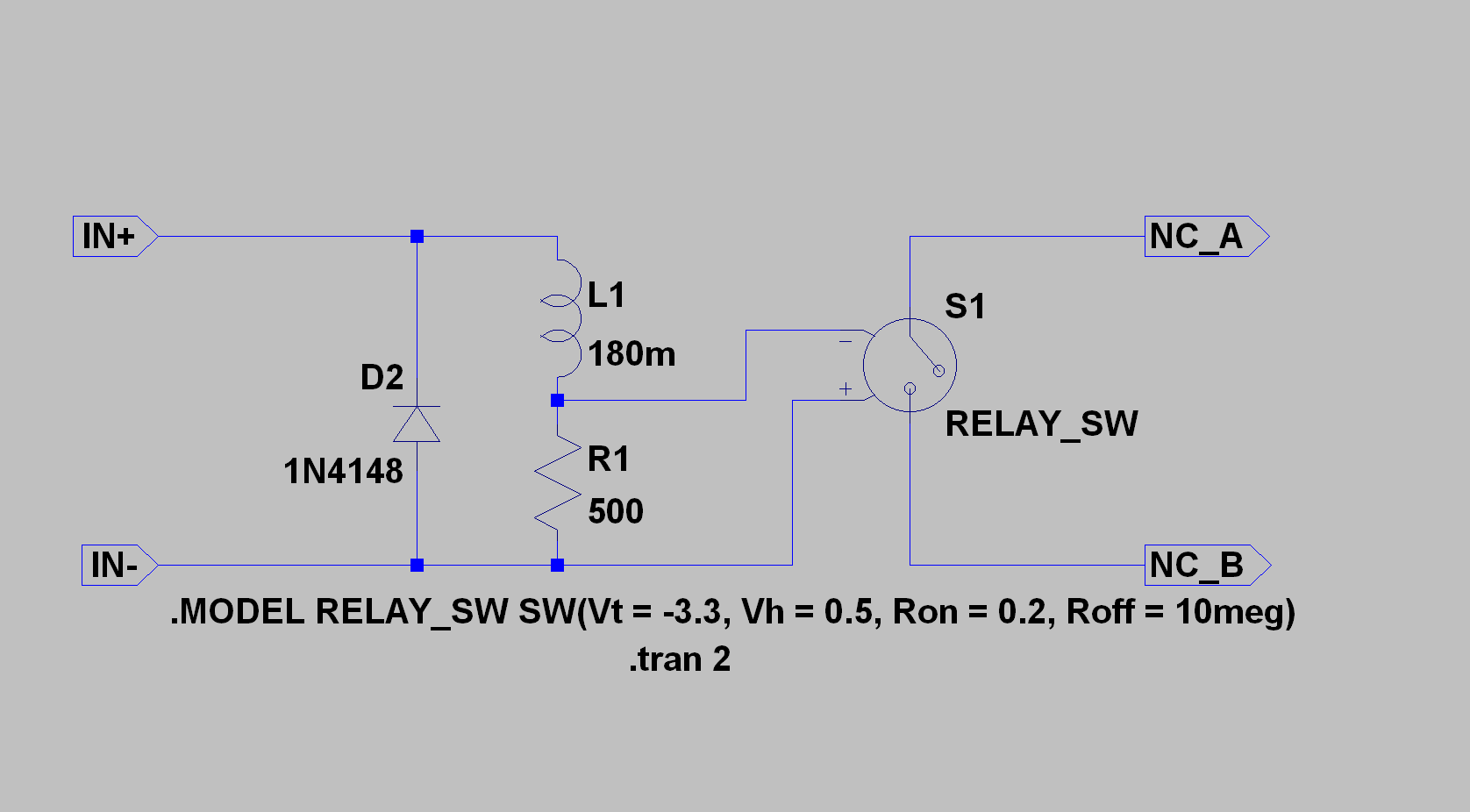

As a two-stage flip-flop, it needs D and Dbar input, and also CLOCK and CLOCKbar as described in the project details. The X{2,3,4,5} components are the relay models. I made a mistake in a previous log that would prevent sequential logic from simulating correctly: the voltage controlled switch should have been across the resistor to simulate the proper delays. Here's the corrected model:

With this, the flip-flop works as intended.

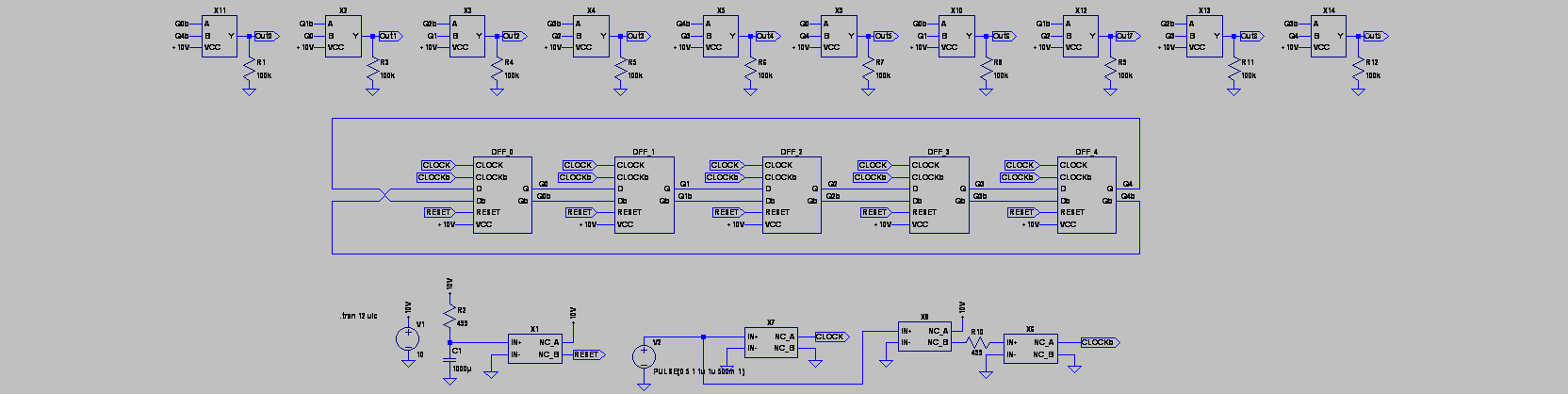

Using the flip-flops, I made a 5-stage Johnson counter which counts modulo-10:

The five flip-flops are in the middle row. On the bottom are four relays for the power-on reset and the clock drivers. At the top are 10 NOR gates to decode the counter states into (10) 1-hot outputs. These could drive Nixie's directly, or feed to diode ROMs for driving 7-segment displays.

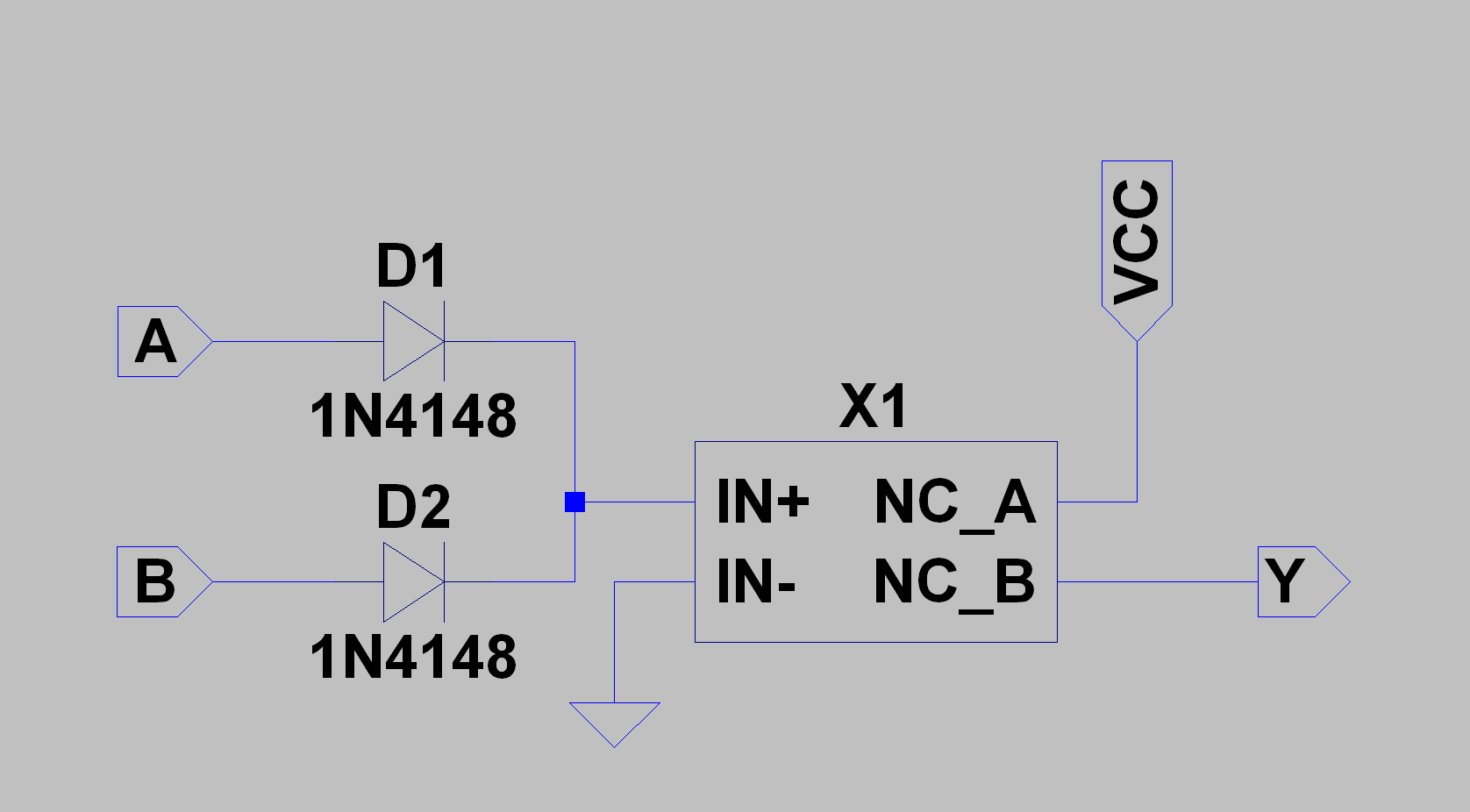

The nor gates look like this:

where X1 is one of the relays.

The states of the Johnson counter at the Q outputs look like this:

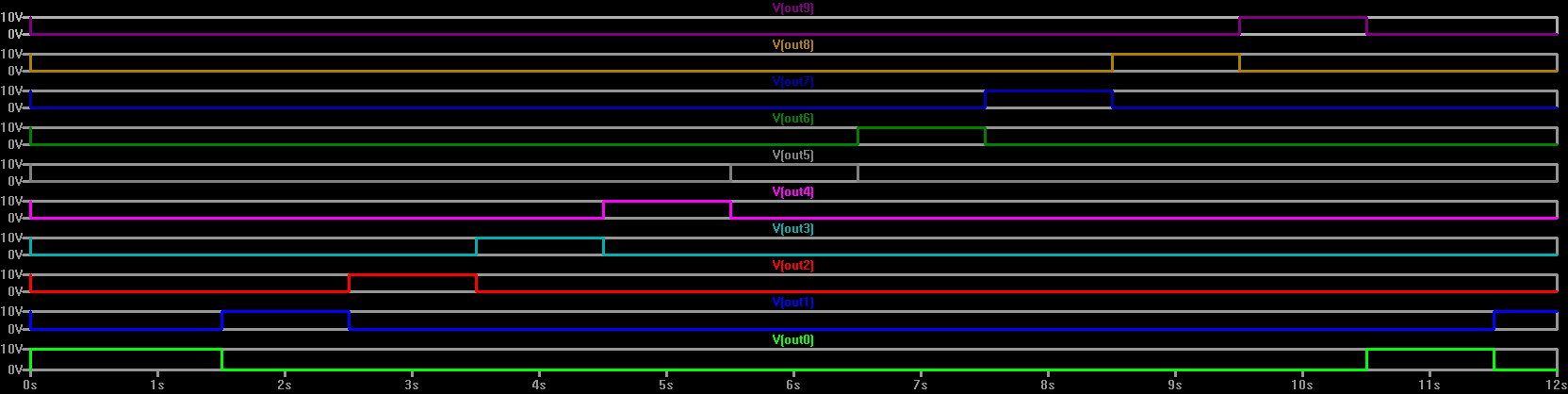

You can see that the counter has 10 states, but they're not much use in this form, so they have to be decoded. That's where the NOR gates come in. The outputs of the NOR gates look like this:

It's a little difficult to parse, but each of the 10 outputs goes high for one clock cycle in turn. This circuit is basically a CD4017 IC made from relays!

I haven't decided what the display will be yet, although I'm considering making my own stepper-motor-like displays that use coils and magnets to rotate wheels with symbols on them. Think of a 6-wheel slot machine that tells time instead of stealing your paycheck.

This would keep the clock more electro-mechanical, which is kind of what I'm shooting for.

If I do this, I won't need the NOR gates for decoding at all. A stepper-type display could be driven from the clock phases directly. The counters would only be needed to divide the clocks for the next stage. A big benefit of this design is that the seconds one digit doesn't need a counter at all, so the clock lifetime should be extended.

Ted Yapo

Ted Yapo

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.