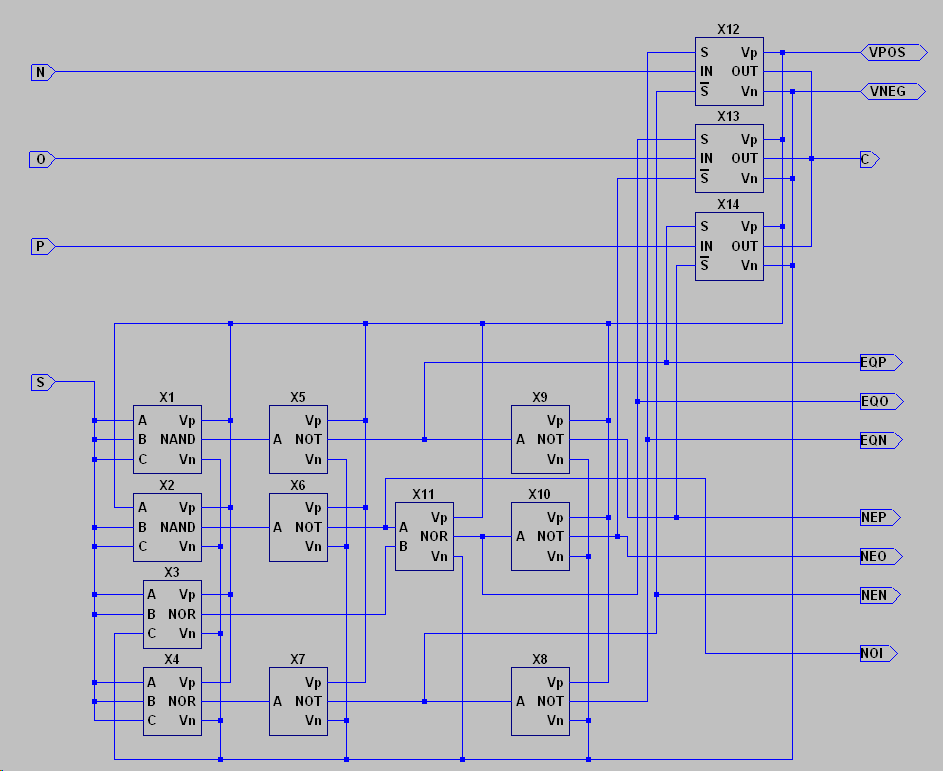

In order to calculate how heavy TRIASIC could be with current limitations let's estimate how compact a ternary selector could be using our library of gates. If you paid attention to this project then you probably remember that ternary selector (multiplexer/demultiplexer) on 1st chip was implemented from binary gates manifesting analog behavior as showed below:

This is how it looked in "spread" form (large squares are "filler cells" that do nothing):

So one ternary selector has:

So one ternary selector has:3-input NAND gates: 2

3-input NOR gates: 2

2-input NOR gates: 1

NOT gates: 6

Transmission gates: 3

TG and NOT gates are "low-profile" gates that could be only 53 units high and 3-input gates have 64-unit height. We can arrange elements in 2 rows - NOT and TG in one row and NAND/NOR in another row.

Width of elements:

3-input NAND gate - 38 units

3-input NOR gate - 38 units

2-input NOR gate - 30 units

NOT gate - 22 units

Transmission gate - 29 units

1st row (NOT and TG): 6*22+3*29=219 units wide and 53 units high

2nd row (NAND and NOR): 4*38+30=182 units wide and 64 units high

Between rows we will have 7+7+3=18 units for 2 metal interconnects, so total height will be 53+64+18=135 units (47um) and total width 219 units (77um) - this is 20 modules from side to side horizontally and vertically we can put 25 rows of such modules (if we allocate space between them for 5 metal lines of interconnects) or totally 20*25=500 ternary selectors.

And at the end one more picture from that 1st chip ;)

SHAOS

SHAOS

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.