The computing unit is fine but I have not even covered the memory aspects.

I'll leave the instruction memory for later, since I'll need quite a bit of it. I'm focusing on Data RAM (less memory needed), and there are 2 memory ports.

I decided to use a unified adress spaces because this saves relays. At first I didn't want to deal with multiplexing, but the amount of relays needed to decode addresses is significant... I will use 16-bits words and see how to make a scalable system, where I can add more bits without changing the whole thing. Hopefully I could reach a few Kbits (one or two hundred words).

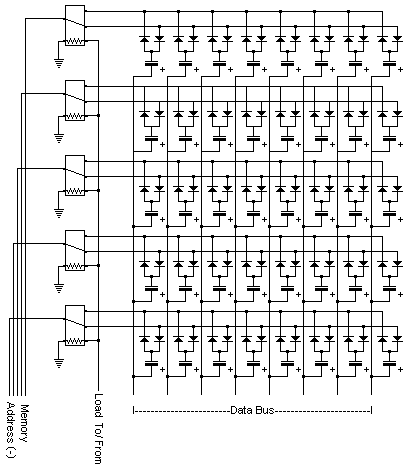

Let's have a look at the capacitor-diodes array (as already developped for the TIM-8 computer). From the website:

Using one relay per bit would be incredibly noisy, power-consuming, expensive and large... OTOH I have to plan for an idle loop that will read (and refresh) each word.

1N4148s cost almost nothing and I can find rather cheap capacitors. On top of that, since I have characterised the relays, I know the triggering parameters and the required current to flip a state under a pre-bias condition.

The TIM page does not tell the capacitance of the array, but I suppose it's somewhere around 100µF. The capacitor must supply enough charge to flip the sense relay and it's about 3.3V and 25mA or something (for how long ?). I am thinking of a way to increase the "kick" by using higher voltages, so I'm looking at 25V capacitors, which is fine is I use 20V for the high fanout control signals. 16V caps are cheaper though...

Of course, all of these suppositions must be tested/verified and TIM's sense and refresh circuits are not explained so I'll have to figure them out.Update: yeah, it was good to test the sensor circuit. No need of 25V capacitors, 3.3V works nicely.

Oh and I probably should think about adding parity protection to the RAM.

Update : this is more complex than that...

The diodes have been removed (this also saves a layer of relays), the type of capacitor is being refined... See the following logs.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Yes, I like the idea of a software refresh loop. I had always thought of a similar thing for a possible diode-logic based computer. You have to be a little more careful writing code and it eats cycles and instruction space, but the hardware is much simpler.

Are you sure? yes | no

I have to see how long the RAM can retain data. It will be interesting. That's why I thought about the parity check. A pure software version will be interesting as well to implement a NMI and dig the gory details of interrupts and context saving.

I love it.

Are you sure? yes | no