We easily assume based on public comment that in general, hardware designers hate (or at least ignore) autorouters.

But scratching into the surface of normal conversations with intelligent, pragmatic hardware engineers and inventors, reveals a common opinion that we would expect in 2018 that autorouting could actually be useful. Problem is, some EDA vendors haven't really done enough to teach users how...

Well, even with somewhat outdated technology, if you know how to set it up you can actually get acceptable, even good, results.

Autorouters are useful not just as an all or nothing proposition either. They can be a tool for the following:

* Iteratively check how good is your component placement and orientations.

* See for a given density and available layers, how hard is this board going to be to route.

* Figure out how many layers you might need.

* Fanout and escape routing)

* etc.

This is a big subject and to be honest, I'm doing this at the request of Sophi Kravitz, and at this beginning stage it feels like I'm about to try and boil the ocean.

Having said that, I am doing this because it needs to be done. I sincerely believe people will benefit from knowledge gained and captured in this project, and I want to encourage others who have experience with vairous automation to contribute. This is not about promoting Altium tools, it's about promoting the acceptance of routing automation and helping everyone get more efficient use out of technology.

PART 1 - RULES abd CONSTRAINTS

The autorouter has to follow design rules and constraints. Obvisouly therefore step one is to configure the design rules. I'm providing here the bare minimum. However usually the bare minimum is all you want - if you over-constrain the design the autorouter will spend a lot of time to give you not much of a result. It's contentions will be higher and completion lower.

Bare in mind - if you can't manually route the design, no automation will be able to either.

Most EDA tools begin a new PCB layout with a set of reasonably conservative rules/constraints by default. This is the case with the tool I'm using for this project (CircuitMaker by Altium). Therefore I am making the assumption you too have a standard set of default rules which is reasonable. So I'm not going to explicitly go over every rule in detail. I'm just going to cover the specific few rules which I use or modify for working with the Situs autorouter in CircuitMaker / Altium Designer. Your mileage may vary.

For those who are "following along" in CircuitMaker, I'm opening a PCB and clicking in the "Design Rules" on the Home ribbon:

Clearance

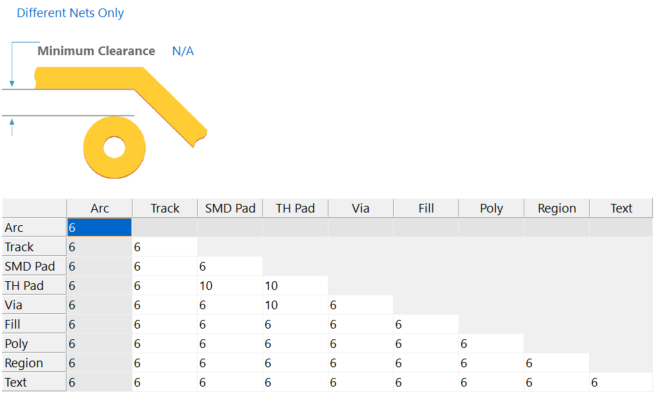

Set up the clearance rules. Autorouters can and will do unexpected things with vias and traces if you don't do this. Electrical clearance at a bare minimum will space things according to an object-to-object table. My defaults are for 10 mils spacing which is way too broad for some of the chips I'm using like the USB UART bridge in this design. Therefore I set all objects to have a default clearance of 6mils (still reasonably conservative for any fab with oil in their lamp). Then I set broader clearance (10 mils) where there will be pads and vias - I don't want those too close together:

KEEPOUT

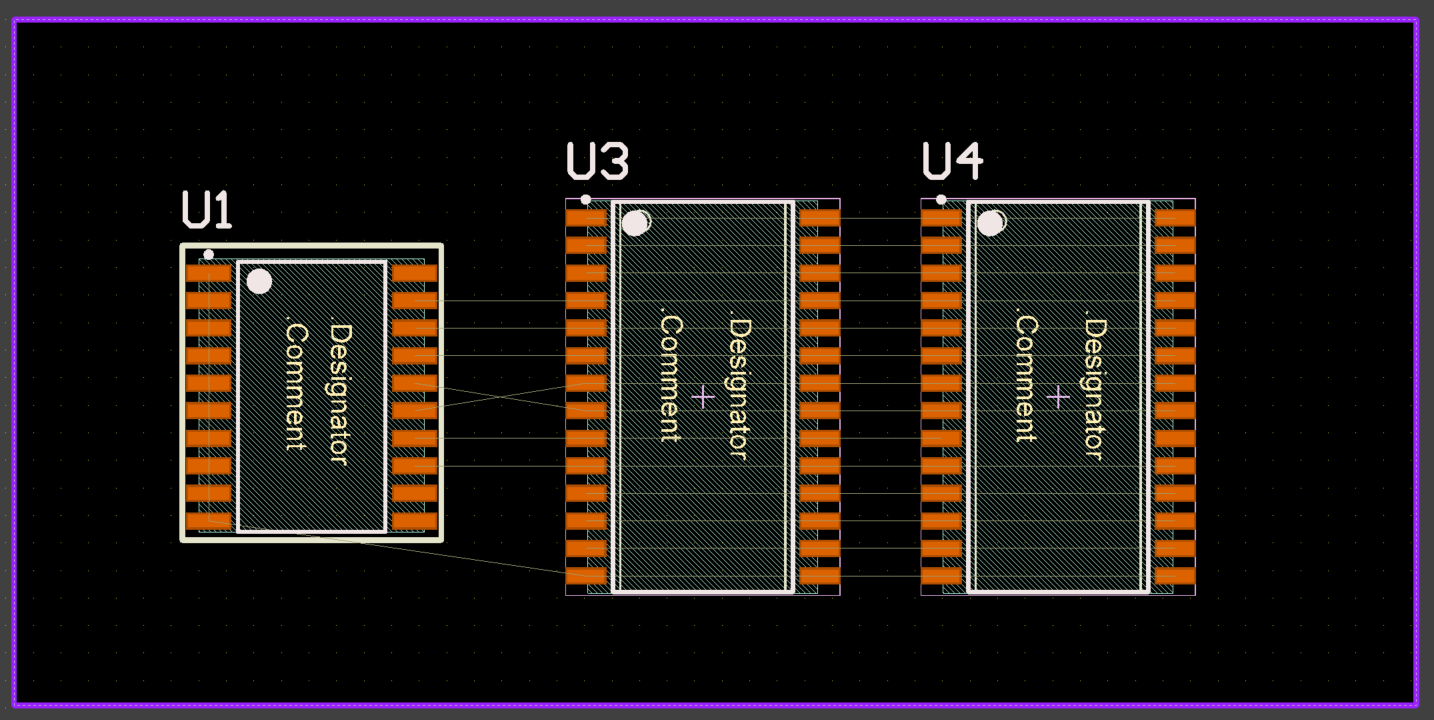

Note that the clearance rule is also applied to "Keepout" objects. Every EDA tool I've messed with has this kind of notion - there are rattle snakes and you must stay away from them! So, for the prupose of a proper demo I am adding a keepout to the basic PCB outline so that routing won't cross the board edge boundary:

Track / Route Width

I also need to use reasonable track widths. The default rule for trace widths is also 10 mil, which is rediculous for power supply nets. (See my other blogs on setting trace width - calculating widths is outside the scope of this project).

I have seen many designs where the designer had several complex rules for trace...

Read more » Ben Jordan

Ben Jordan