Chip prototyping used to be prohibitive for small startups and academy until services like MOSIS brought down prices to few thousands dollars per mm2 -in technology nodes capable to run circuitry at moderated performance-. MOSIS runs a multi-project wafer service that aggregates multiple designs onto one mask set to reduce prototyping costs. This aggregation restricts minimum sizing to few millimeters bringing down prices from hundred thousand to few thousand dollars.

However, as an example, five thousand dollars budget for a college in a developing country might be a big number. It is definitely a huge number for a tinkerer or an engineer student ambitious enough to leap from the discrete world to the integrated planet. A service capable to deliver a chip for hundred dollars would break a paradigm and place a bridge to a community always hungry of new chips.

Although getting a chip designed is not as easy as getting a board layout, it might be a reasonable path if you get the required tools and support to get it done. For instance, at most of VLSI graduate programs, making a chip is a tortuous route considering the lack of support and libraries. At grad school, the lack of pads, basic blocks and digital support, make mostly 90% of the work required to prototype your circuit ideas. Having a chip platform where you just can plug your supply nodes, digital calibration data, input and output signals, would bring down chip design from several months to a few weeks.

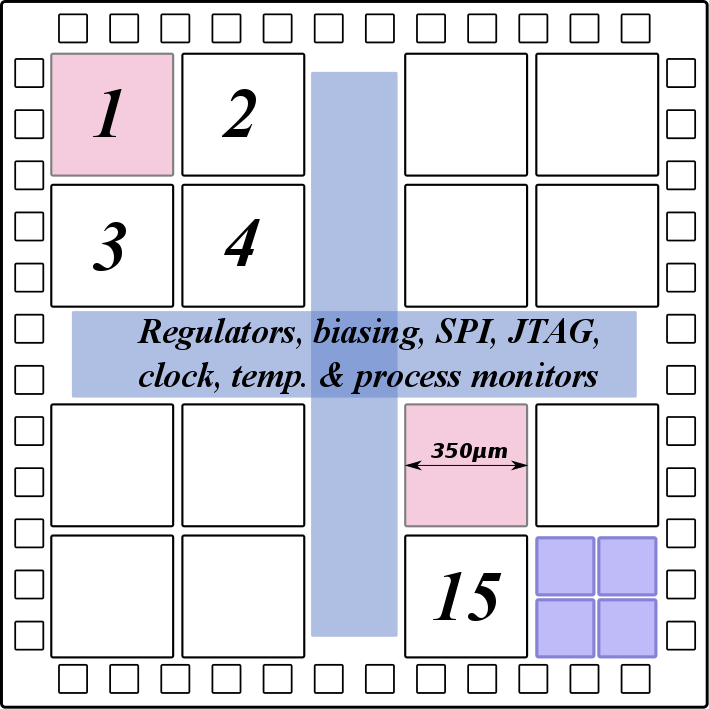

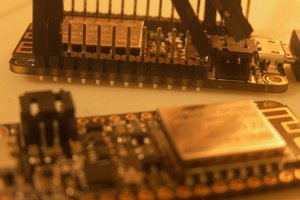

Itsy-chipsy is a chip platform with the required basic blocks to get a chip done. A platform with onchip regulators, voltage references, current sources, pad library, SPI, JTAG, clock generators, temperature and process monitors.

These utility blocks are placed on the chip to service blocks designed by users of the service. With this chip platform, we paved the way to a multi-block service like-oshpark capable to offer silicon area for your own chip, for as low as hundred dollars.

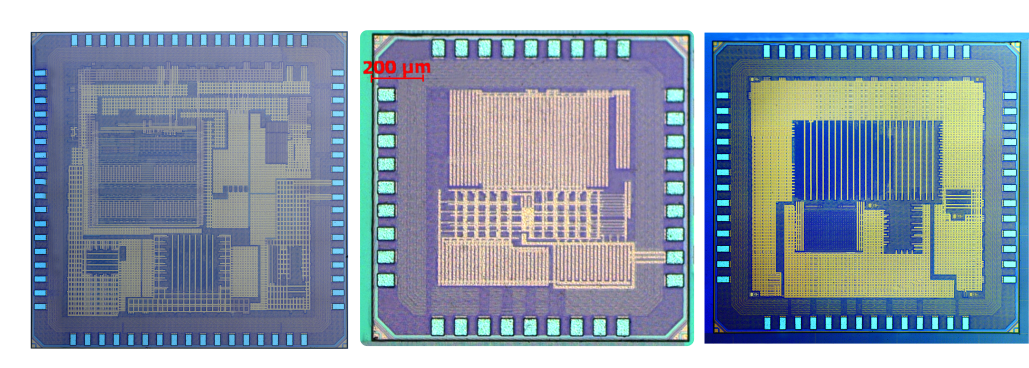

The itsy-chipsy platform has been partially implemented on chips with several blocks:

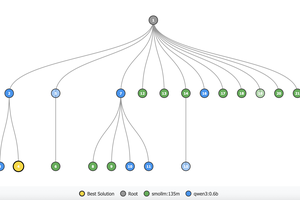

We are working on the second version of the platform and we are expecting by the end of summer, preliminary results should be reported. By September 2018, prototype chips would be available for demos. The second version aims to service a 16 multi-block chip. For instance on a 2mm by 2mm chip in 180nm CMOS technology, 16 blocks of 350umx350um can be instantiated. Where for each 350umx350um block, the fabrication cost will be 350 dollars. Each block will have access to supply pins, SPI, JTAG, regulators, biasing, so the 350umx350um are full real-state for your circuitry. To give some perspective, you might place a basic 32-bit RISC-V-based microprocessor with the basic instruction set on that area. You will have thousands of transistors available for you to get your idea on-a-chip!

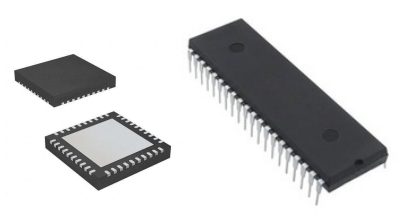

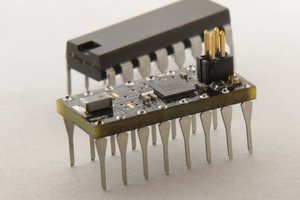

A 350umx350um block can be splitted in four, bringing down the price to 100 dollars per a 170umx170um block. A 350umx350um user can get 2 fully packaged chips in DIP 40 pins package or 2 QFN packages with 40 pins 5mmx5mm 0.4mm pitch. A tinker ambitious enough can get her/his own packaged chip for just 100 dolllars!

Couple of foundries are interested and are fully supporting us to get this kind of model ahead. After the platform chip is fully qualified, and current open-source tools are enabled for the technology node, we foresee a crowdfunding campaign for the first oshpark-like chip in 2019.

We are the team behind the open-source 32-bit microcontroller. A chip with the RISC-V instruction set and built-in with peripheral...

Read more » Onchip

Onchip

JohnsonFarms.us

JohnsonFarms.us

Philip

Philip

Alexander

Alexander

darkspr1te

darkspr1te

we are trying to setup a small scale fab ,how this can help us ?