The Weird CPU (TTA8)

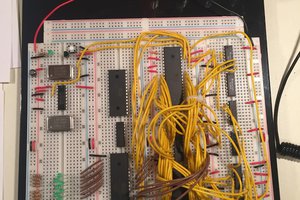

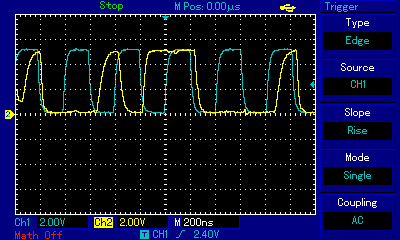

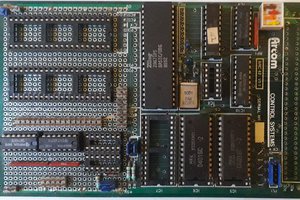

Here is my 8 bit Weird CPU (https://hackaday.io/project/12879-weird-cpu) in action (playing LED Light Chaser):

When programming, the bottom (red) LEDs are for the memory address entry, and the top (yellow) are for data entry. The extra switch on the left of the top row is the reset button.

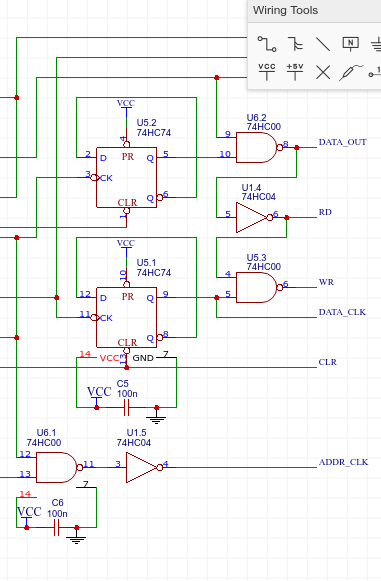

Micro-Code and Micro-Programming

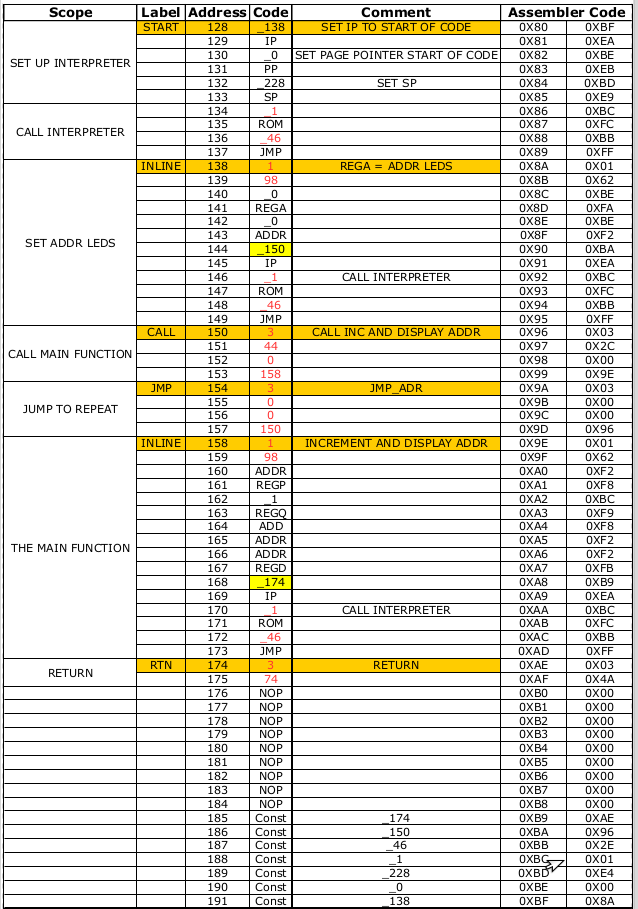

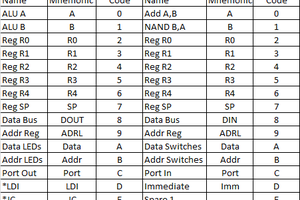

The TTA8 instruction set is very minimal:

- Move Fetch_Address to Deposit_Address

With the Input/Output (I/O), Program Counter (PC) and ALU embedded in the address space, we also have:

- Unconditional Jump

- Jump On Carry

- ADD

- NAND

- Input/Output

The input/output registers (REGA and REGD) are used by the Front Panel.

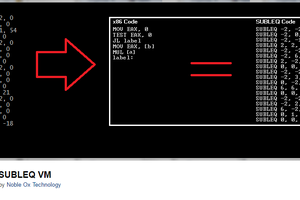

The TTA8 native instruction set is not very OpCode like, that is why the CPU is called Weird! The native instruction is It is best described as micro-code. And coding micro-code is often called micro-programming.

The major limitation for the TTA architecture is that the code density is very low. It takes a lot of instructions (or a lot of hardware) to do anything useful. The purpose of an interpreter is the increase the code density, to make the code look move conventional or OpCode like. The cost of this is execution speed.

The TTA8 just does not have enough memory (without paging) to develop a serious interpreter, but the code developed will run on a 16 bit TTA (TTA16) providing the architecture is similar. So it makes a good test bed to get an idea of what is possible.

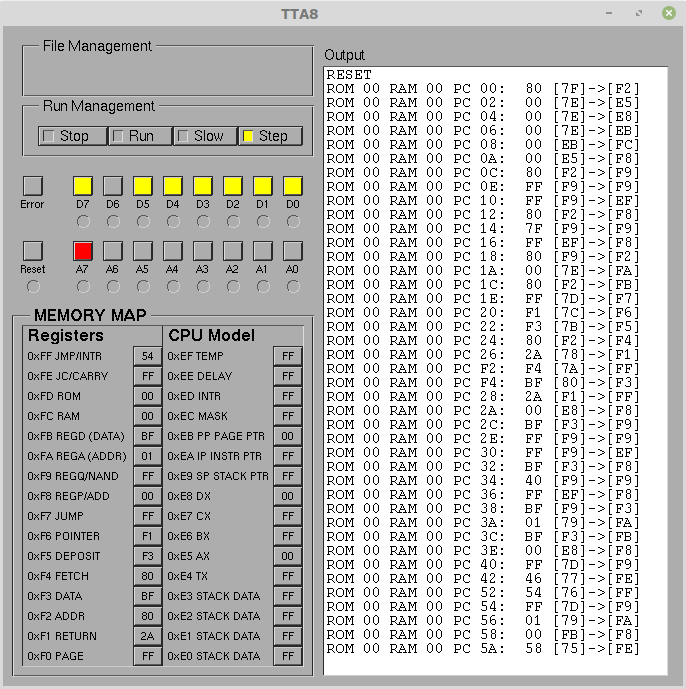

Proposed Memory Mapping

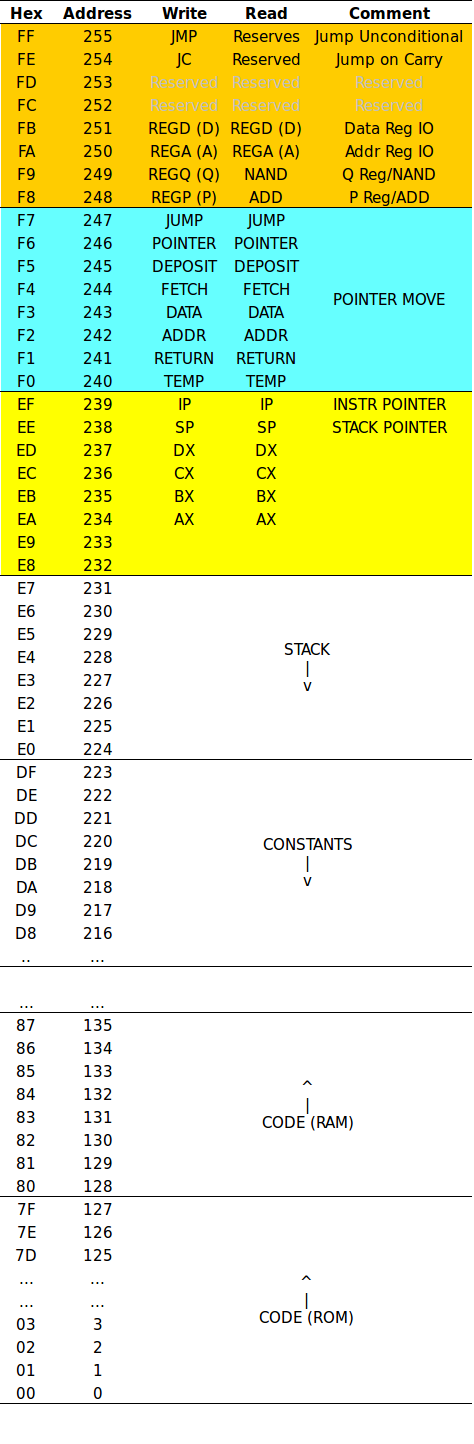

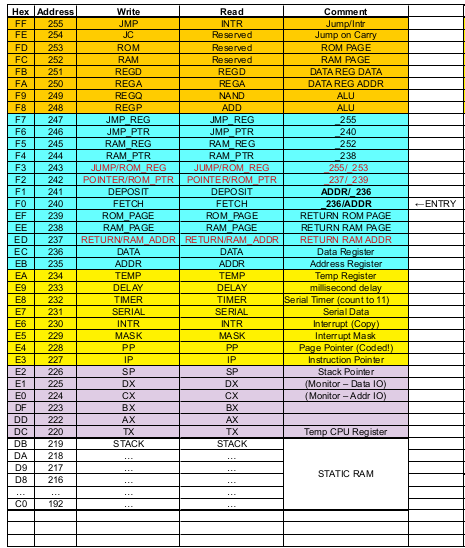

Here is the basic memory map of the TTA8:

Starting from the top:

- Hardware registers:

- Unconditional jump

- Jump on carry

- Front panel data register (I/O)

- Front panel address register (I/O)

- ALU: Q register (write) or NAND register (read)

- ALU: P register (write) or ADD register (read)

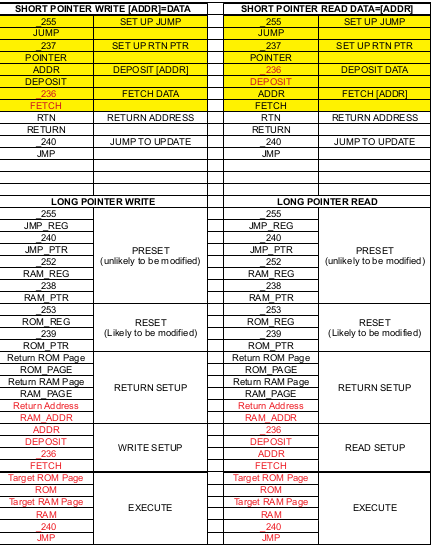

- Indirect addressing (i.e. pointer move)

- The TTA architecture uses self-modifying code for indirect addressing

- CPU Model:

- Instruction Pointer (IP)

- Stack Pointer (SP)

- Other registers (proposed)

- Stack

- Program constants

- Program code (ROM)

- Monitor code (ROM)

The Interpreter

An interpreter allows the CPU to emulate OpCodes and there by increase the code density. The cost to this is speed. An interpreter is very roughly 10 times slower than native code. Actually it is much slower because the Interpreter has other house keeping duties, such as managing the Interrupts.

Update

After many months of working on this project it is time to de-clutter.

AlanX

agp.cooper

agp.cooper

Keith

Keith