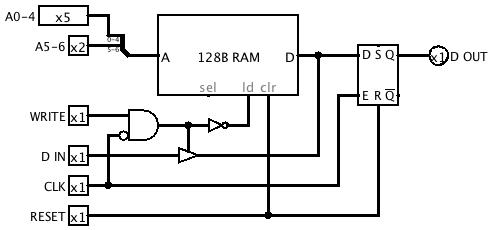

I replaced the output flip flop in the register file subcircuit with a transparent latch. This is mainly to aid debugging, so I can pause the simulation during phase 1 of a bit cycle and see the data read from the registers.

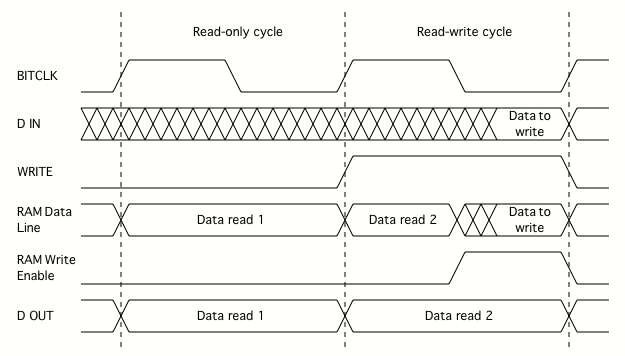

Revised timing diagram:

I replaced the output flip flop in the register file subcircuit with a transparent latch. This is mainly to aid debugging, so I can pause the simulation during phase 1 of a bit cycle and see the data read from the registers.

Revised timing diagram:

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.