If you are here for a refresher on digital logic, you might have had a traditional class sometime in the past. It might surprise you that we haven't talked about Karnough maps (K-maps) or Quine McCluskey diagrams. It turns out that since we are preparing for FPGAs, these things aren't so important. To understand why, you have to look back at the history of digital electronics.

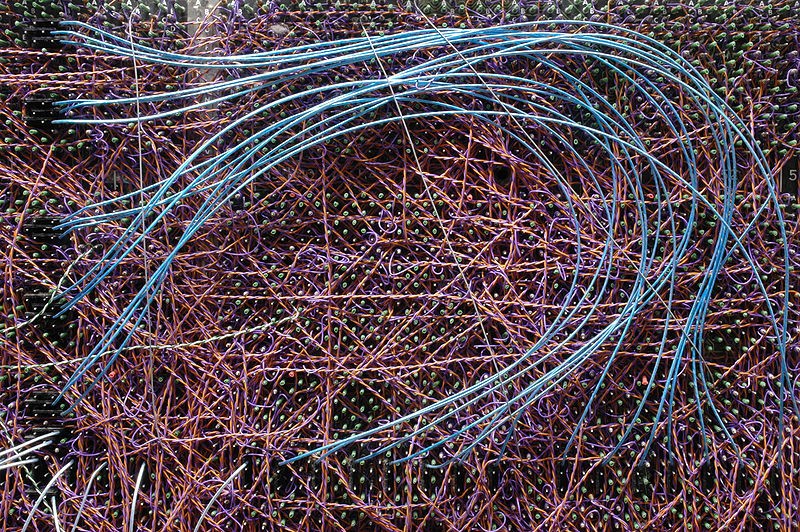

Early logic circuits used relays, tubes, and transistors to build logic circuits. It is true that you could custom build anything you wanted, but smart designers realized that wasn't efficient so instead they would make a card with a few gates on it. For example, I might make a card with 6 two-input NOR gates on it. Then I would have a backplane full of cards. My goal, then, was to figure out how to make everything out of two-input NOR gates. That led to things like this Digital Equipment Corporation backplane:

(Photo credit: Dave Fisher Creative Commons Attribution-Share Alike 3.0)

Later, you could get ICs that had different kind of gates to them. Now optimizing to one kind of gate wasn't as important as minimizing down to the least number of packages. With FPGA design, you actually have gone back to the old days. There's generally just a few types of circuits available on the FPGA. There's just lots of them. But instead of a backplane, the connections are made with some sort of configuration memory. The circuits, though, are usually much more complex than just a NOR gate.

Luckily, the HDL compilers will handle all of that for us. We can describe what we want and -- mostly -- you don't have to be very concise or efficient. Well, at least until you do have to. There are certain "bad practices" we'll talk about in future bootcamps that can lead to bad FPGA designs. But for the most part you can describe what you want even in a very high-level way and the compiler will figure out how to make the virtual spaghetti backplane you need.

Al Williams

Al Williams

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.