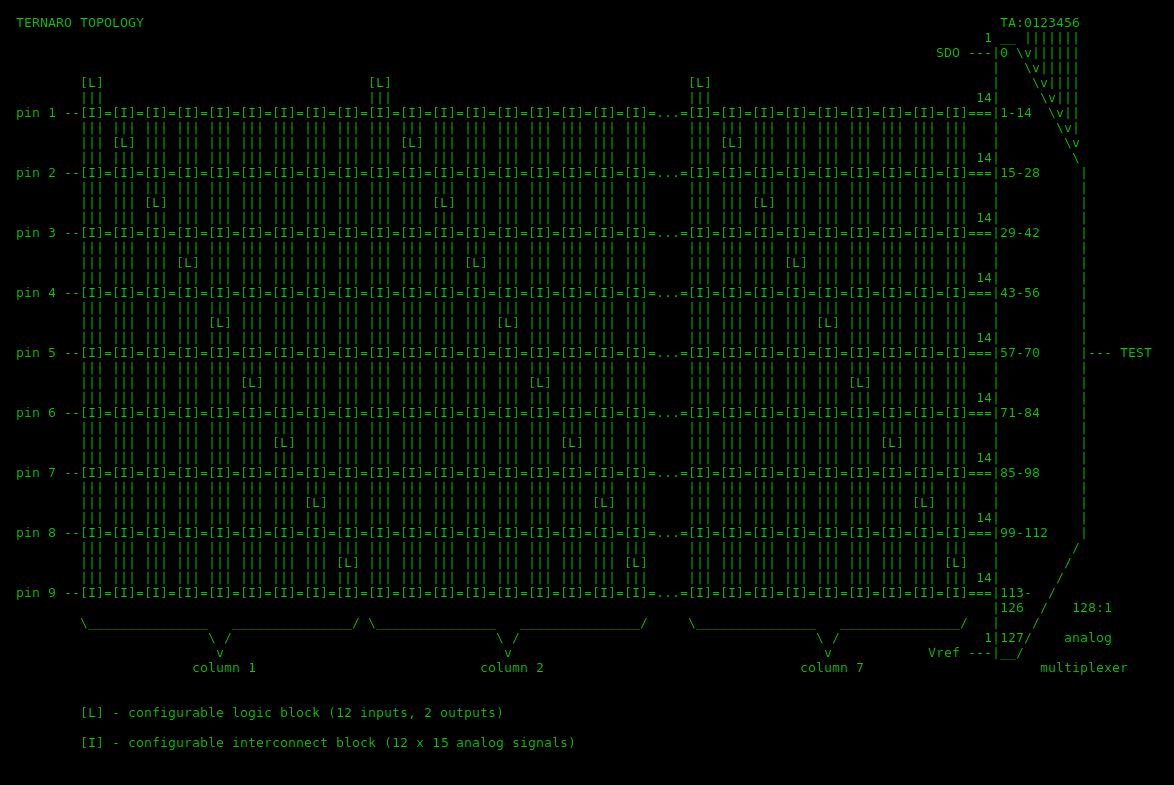

This is how I imagined TERNARO from inside:

Bitstream should define every column one by one (from left to right) with every channel in the column (from top to bottom) like L-I-I-I-I-I-I-I-I-I (4+6*9=58 bytes per every channel/column intersection).

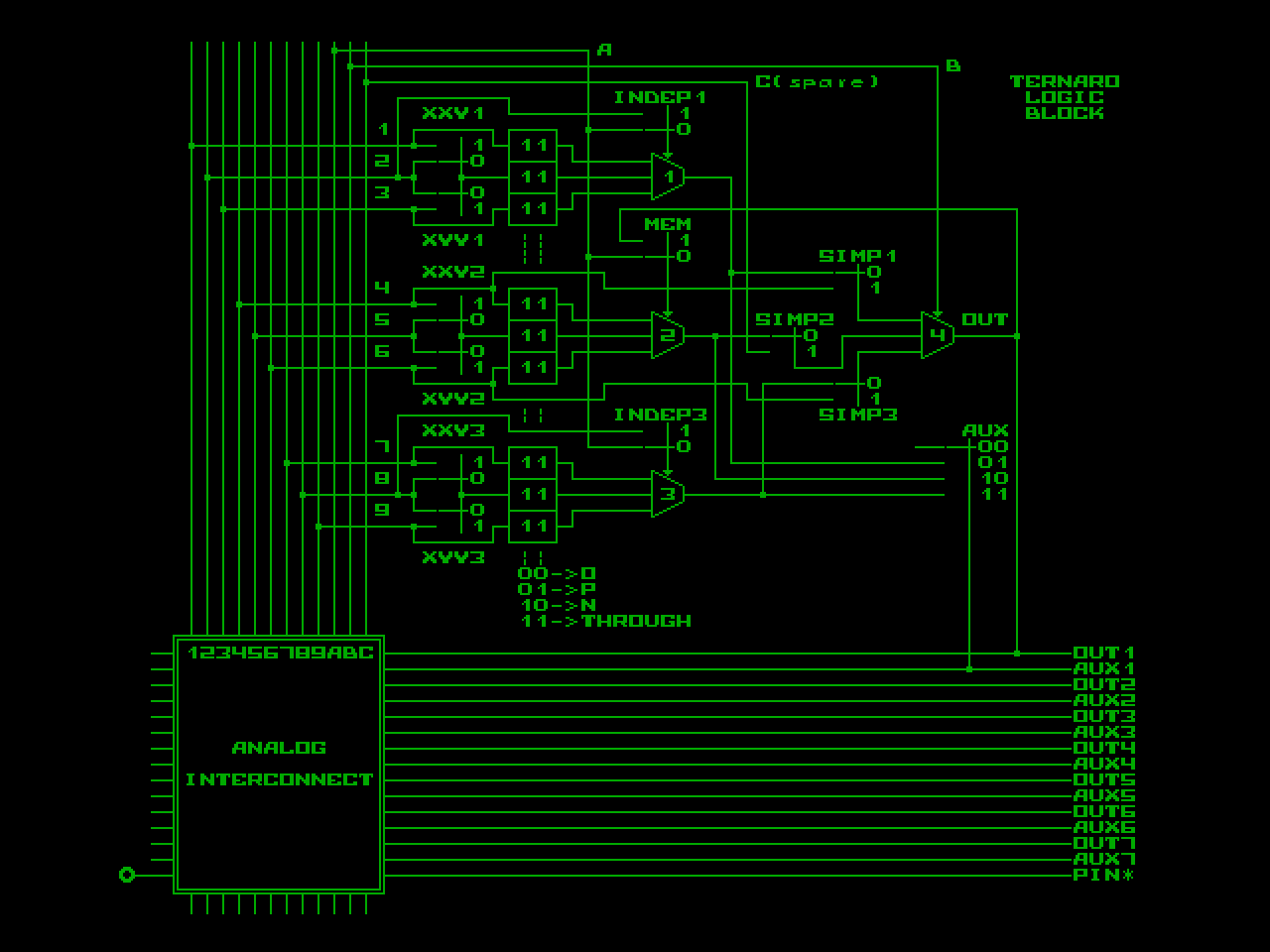

Every interconnection block [I] behaves as 12 switches with 16 positions each (position #0 means no connection):

And every logic block [L] looks like this (with nearest interconnect showed as well):

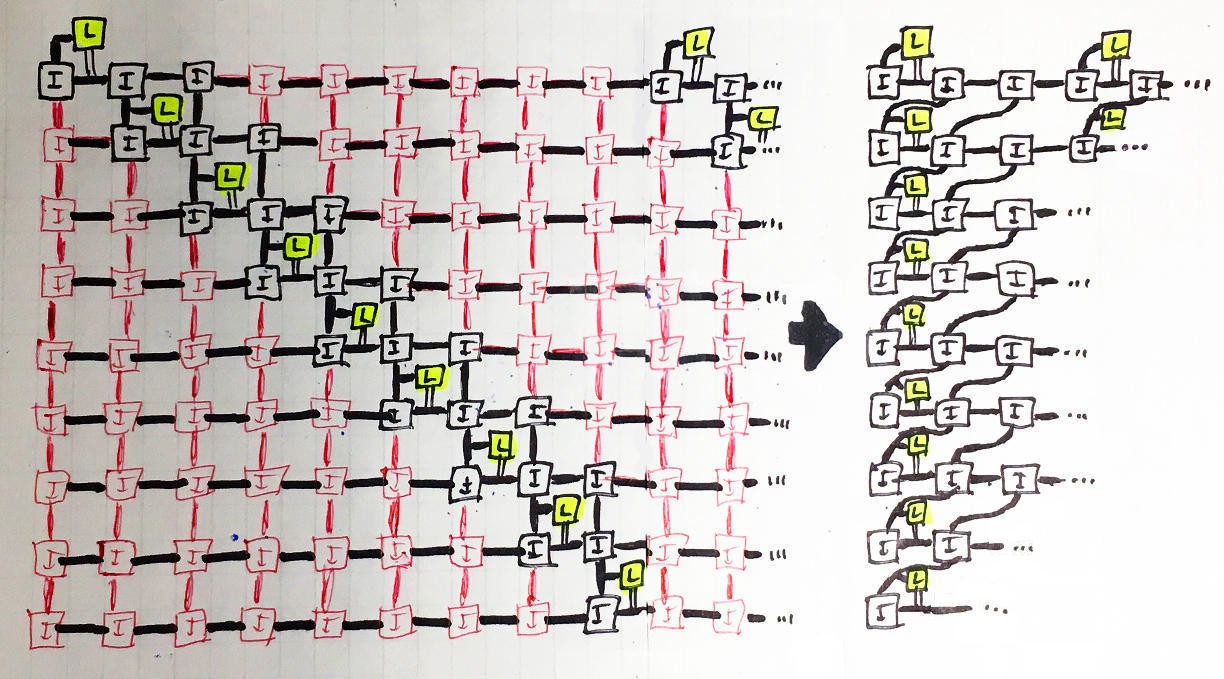

Approach when adding another pin (and another horizontal channel) requires additional interconnect block in every channel for every column is not very scalable. So later I can do some reduction like showed below:

In this case it will scale linearly with adding more pins. How many diagonals with interconnects can be removed to still be flexible for most real life applications? Honestly I don't know. Probably I need to write synthesis/place&route software first and see how it goes with different numbers. This is how one of the most extreme cases of reduction can look:

SHAOS

SHAOS

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.