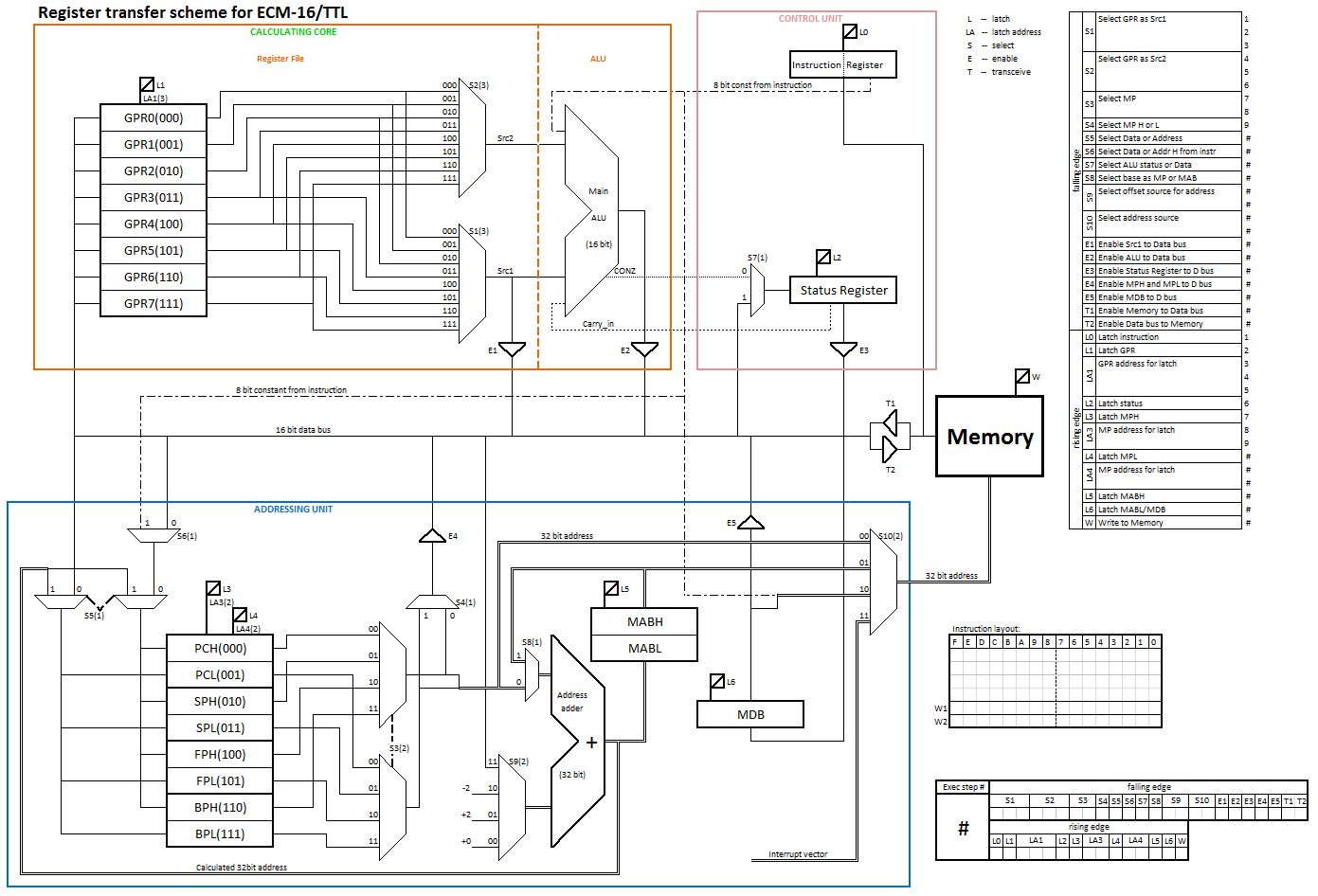

After starting designing micro-instruction sequences for memory access operations, I encountered some difficulties with the scheme presented in previous log entry. Thus I had to modify this scheme; the modifications were not very big though.

Following changes were made:

1) added 16-bit Memory Data Buffer register -- its primary use is to temporarily store direct offsets;

2) final address source selector was widened from 1-of-2 to 1-of-4, so that all needed address sources are available;

3) added selector of base address source - now base address can be in Memory Pointer, or in Memory Address Buffer -- this is most useful in multi-word data transfers between registers and memory.

Below is the scheme itself, and after it there are some notes about it:

(By the way, the Excel turned out to be quite useful as line drawing tool for creation of the above scheme)

Register layout and function:

There are 16 addressable registers in 2 blocks, 8 General Purpose Registers (GPR) and Memory Pointers (MP). Each group has dedicated arithmetic unit, for GPR this is 16-bit Main ALU, for the Memory Pointers it is a 32-bit adder.

There is also the 16-bit Instruction Register, which holds currently executed instruction, 16-bit Status Register, which is very special in that its bits can be set and cleared independently, and which is manipulated in its own special way, 16-bit Memory Data Buffer, which is used in some kinds of memory access operations, and 32-bit Memory Address Buffer, which is the source of address in most of the memory access operations.

Busses:

There are 3 main busses --

1 - the 16-bit Main Data Bus, it is used for general data exchange,

2 - 32-bit Address Bus, providing address for accessing memory location,

3 - 16-bit Instruction Bus, that is kind of offshoot of the main bus, but can be cut off, so some register transfers can be combined with the fetching of new instruction.

Pavel

Pavel

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.