Disclaimer: Use the information provided here at your own risk. I do not take any responsibility for any resulting damage.

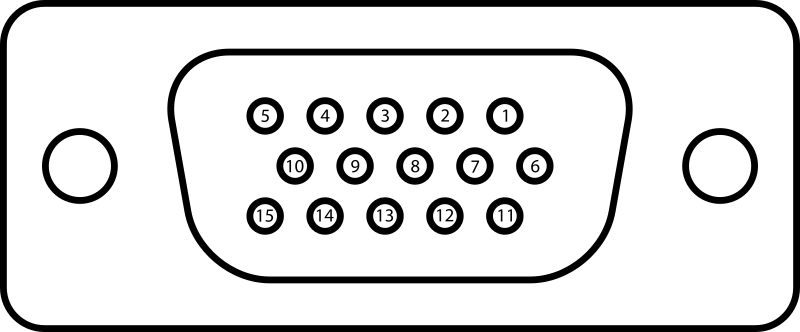

1 Pin outs

PIN # |

name | description |

|---|---|---|

| 1 | RED | Red video |

| 2 | GREEN | Green video |

| 3 | BLUE | Blue video |

| 4 | ID2/RES | formerly Monitor ID bit 2, reserved since E-DDC |

| 5 | GND | Horizontal sync ground |

| 6 | RED_RTN | Red return |

| 7 | GREEN_RTN | Green return |

| 8 | BLUE_RTN | Blue return |

| 9 | KEY/PWR | formerly key, now +5V DC, powers EDID EEPROM chip on some monitors |

| 10 | GND | Vertical sync ground |

| 11 | ID0/RES | formerly Monitor ID bit 0, reserved since E-DDC |

| 12 | ID1/SDA | formerly Monitor ID bit 1, I²C data since DDC2 |

| 13 | HSync | Horizontal sync |

| 14 | VSync | Vertical sync |

| 15 | ID3/SCL | formerly Monitor ID bit 3, I²C clock since DDC2 |

Table 1: Pin out of a female DE-15 connector functioning as a VGA output from wikipedia

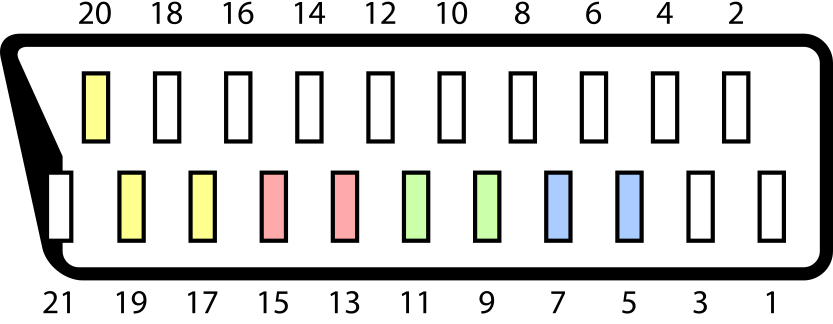

PIN # |

description |

|---|---|

| 1 | Audio output (right) |

| 2 | Audio input (right) |

| 3 | Audio output (left/mono) |

| 4 | Audio ground |

| 5 | Blue ground |

| 6 | Audio input (left/mono) |

| 7 | Blue |

| 8 |

Status & Aspect Ratio 0–2 V → off +5–8 V → on/16:9 +9.5–12 V → on/4:3 |

| 9 | Green ground |

| 10 | not used in this project |

| 11 | RGB Green |

| 12 | not used in this project |

| 13 | Red ground |

| 14 | pin 8 ground |

| 15 | Red |

| 16 |

RGB selection 0–0.4 V → composite 1–3 V → RGB |

| 17 | Composite sync ground |

| 18 | pin 16 ground |

| 19 | Composite sync output |

| 20 | Composite sync input |

| 21 | Shell/Chassis |

Table 2: Pin out of a SCART connector from wikipedia

2 Power source

Many components used in this project require a 5V power source. You have several alternatives:

- If you are generating the VGA signal using a PC you can get it from its internal power supply. You can see the pin out here.

- If the system used to generate the VGA signal has USB ports you can get it from one of them. You can see the pin out here.

- You can use an external power supply. Any cell phone charger with an USB connector should be adequate.

- If the device generating the VGA signal is not very old it will probably provide 5V through the pin 9 of the DE-15 connector. If it complies with the DDC host system standard it will supply at least 300 mA, which is enough to power all the components used in this project.

3 Horizontal frequency monitoring

As mentioned, the frequency of the horizontal scanning of a CRT TV is about 15.7 KHz. If the frequency composite sync signal is higher the image will not be properly displayed, but it will probably not damage your TV since the actual scanning movement of the electron beam is directed by internal deflection generators. However, if you are using a very old monitor or just do not want to be annoyed by a messed image you can use a circuit to blank the screen when the horizontal frequency is not correct. You can see these circuits in Tim Worthington's guide. I have not tested it, but I suggest you to use the solution based on the PIC12C508 since it has only a few connections to solder. The PIC will monitor the horizontal sync signal and will generate a logic output called ENABLE. If the horizontal frequency is OK the PIC will set ENABLE high. Otherwise it will set it low. This ENABLE signal can be used in several ways:

- Blank the screen by setting the RGB selection signal to ground when the frequency of the horizontal sync signal is wrong

- Disable the composite sync signal when the horizontal sync frequency is too high

- If a DC-DC converter is used to generate the status signal, shut it down

The use of the ENABLE signal is described bellow.

4 Connections

4.1 Common ground

The HSync ground (VGA pin 5), VSync ground (VGA pin 10), ID0/RES (VGA pin 11), composite ground (SCART pin 17), RGB selection ground (SCART pin 18) as well as the ground of the DC-DC converter and/or external power sources (if used) must be wired together.

4.2 RGB signals

You must connect the VGA red (VGA pin 1) to the SCART red (SCART pin 15), the VGA green (VGA pin 2) to the SCART green (SCART pin 11), the VGA blue (VGA pin 3) to the SCART blue (SCART pin 7), the VGA red return (VGA pin 6) to the SCART Red ground (SCART pin 13), the VGA green return (VGA pin 7) to the SCART green ground (SCART pin 9) and the VGA blue return (VGA pin 8) to the SCART blue ground (SCART pin 5).

4.3 Sound signals

You must connect the analog audio groud of your system to the SCART audio ground (pin 4). The left and right audio signals of your system must be connected to the SCART left and right audio inputs respectively. These are the pins 6 and 2 of the TV SCART connector respectively. However, if you are making your adapter using a female SCART connector and a standard SCART cable you must take into account that it has some wires crossed. In that case you must connect the left and right audio signals of your system to the left and right audio outputs of the female SCART connector of your adapter (pins 3 and 1) respectively.

4.4 Sync signals

When a field is being drawn, the SCART composite sync signal is normally 0.3V, and there are pulses to 0V during the horizontal blanking intervals. The polarity of the pulses are inverted during the vertical blanking intervals. This composite sync signal must be generated from the horizontal sync signal (VGA pin 13) and the vertical sync signal (VGA pin 14) and connected to the SCART sync input. This is the pin 20 of the TV SCART connector, and has an impedance of 75Ω. Again, if you are making your adapter using a female SCART connector and a standard SCART cable you must take into account that it has some wires crossed. In that case you must connect the generated composite sync signal to the sync output of the female SCART connector of your adapter (pin 19). The composite sync signal is generated in different ways depending of the polarity of the horizontal and vertical sync signals.

4.4.1 The vertical and horizontal sync signals have different polarity

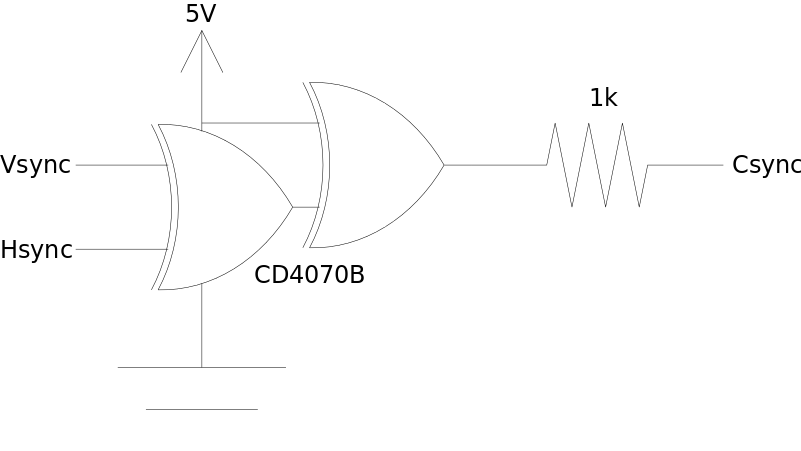

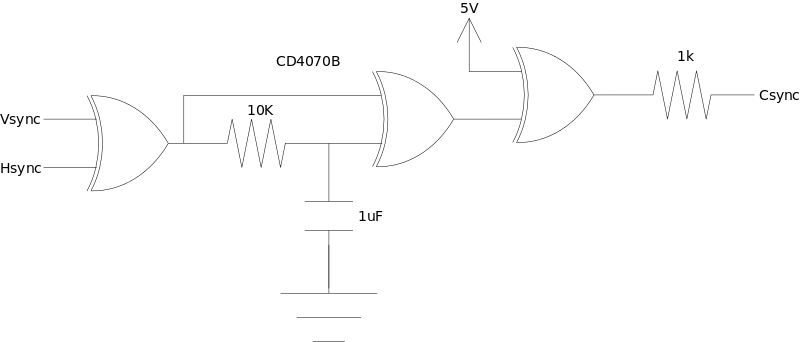

In this case you can generate the composite sync just by xording the horizontal and vertical sync signals. For example you can use one of the four XOR gates of a CD4070B chip to make this circuit:

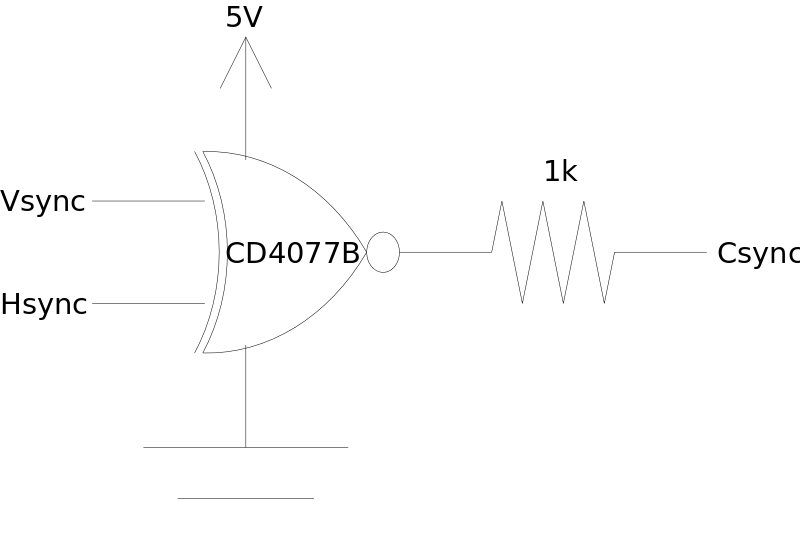

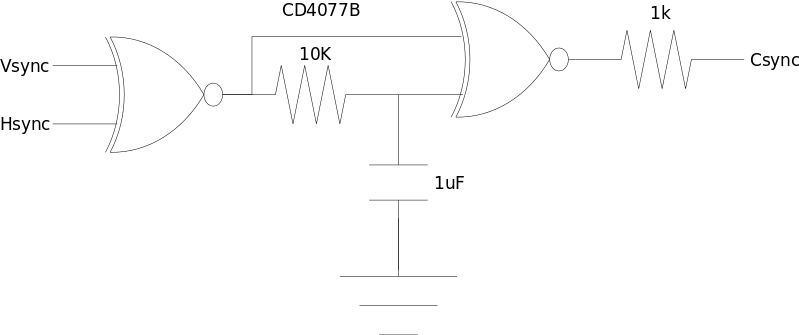

The resistance is necessary to reduce the H level of the composite sync signal to 0.3V approximately. Note that it is a bad idea to leave the inputs of the remaining CMOS gates floating. You should connect them to 5V or ground so you must solder a total of 12 connections. If you have XNOR gates instead of XOR gates (for example a CD4077B chip) you can solder a bit more and use this circuit:

4.4.2 The vertical and horizontal sync signals have the same polarity

In this case the composite sync must be the complement of the exclusive OR of the horizontal and vertical sync signals. You can generate it using a CD4077B chip in this way:

Again you should not leave the inputs of the remaining gates floating. Alternatively, you can use XNOR gates as shown in this circuit:

4.4.3 You do not know or you do not want to care about the sync signals polarity

In this case you can use any of these circuits:

They are very similar to the circuit of Tim's guide, but they use only one capacitor and one resistor to adjust the polarity.

Notes

- I have not tested any of the circuits described in this subsection. Instead I generated the composite sync signal using the circuit described in section 5.

- It is always advisable to place decoupling capacitors as close as possible to the chip containing the logic gates.

- If you want to use the ENABLE signal to disable the composite sync signal when the horizontal frequency is wrong, you will have to modify the circuit as described in Tim's guide. For example you can use the following circuit:

![]()

4.5 Status & Aspect Ratio

You can leave the SCART pin 8 unconnected, but you will have to select the SCART input of your TV manually. If you want the TV to switch to the SCART input automatically, pin 8 voltage must between 9.5V, and 12V (or between 5V and 8V to indicate an aspect ratio of 16:9 in some TVs). Again you can get 12V in several ways:

- If you are generating the VGA signal using a PC you can get it from its internal power supply. You can see the pin out here.

- You can use an external power supply.

- You can use a tiny DC-DC converter

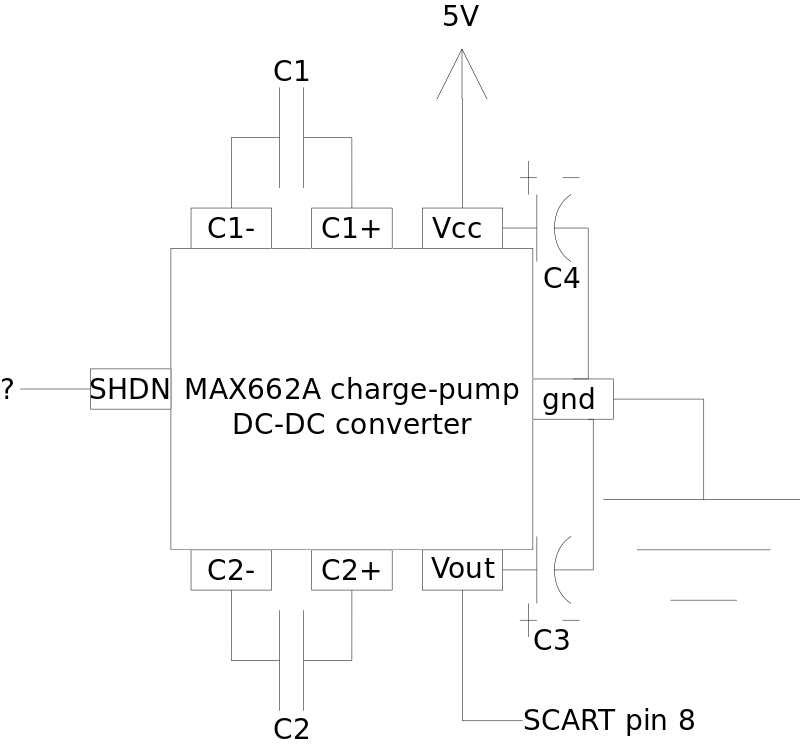

I chose the last option to minimize the number of external connectors of the adapter. I used a MAX662A in this way:

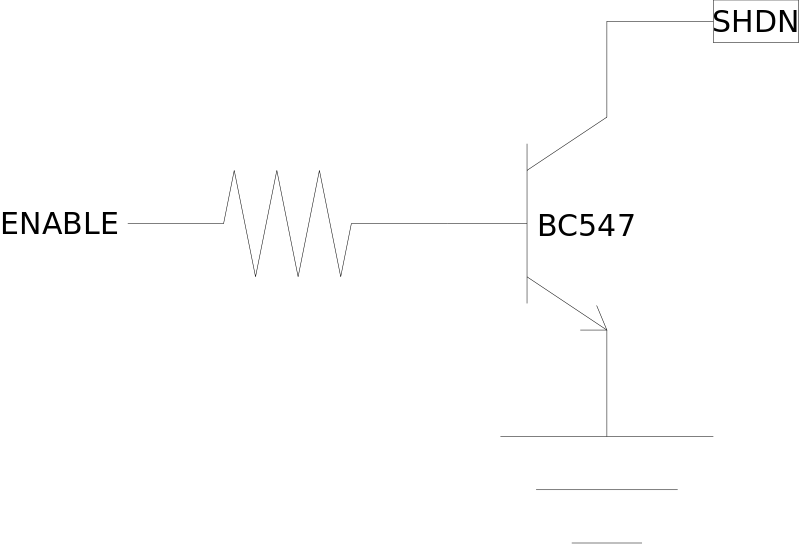

C1 and C2 must be ceramic or tantalum capacitors and their capacitance should be in range 0.22μF-1.0μF. The capacitance of C3 and C4 should be at least 10μF (or 2 μF if they are ceramic capacitors). SHDN is an input signal that is internally pulled up to Vcc. You can connect it to ground and the converter will be always working. Alternatively, you can use the ENABLE signal to activate the converter only when the horizontal frequency is OK in this way:

According to the documentation, the SHDN pin current in shutdown mode is not greater than 50μA so a resistance value of 9MΩ or less should be adequate. Note that I have not tested this since I generated the SHDN signal using the circuit described in section 5.

4.6 RGB selection

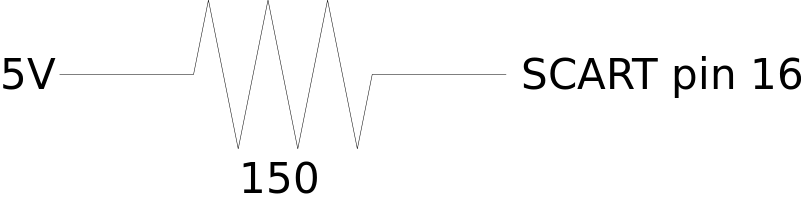

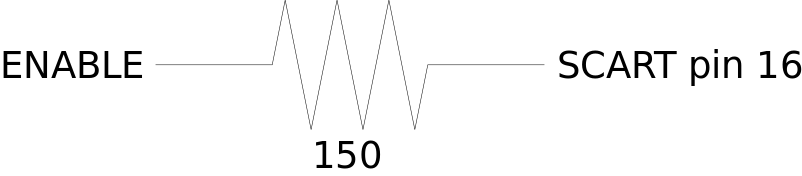

The voltage of the SCART pin 16 must be between 1V and 3V to select the RGB mode. This pin has an impedance of 75Ω so you can get it just by doing the following connections:

Alternatively, if you want the screen to be blanked when the horizontal frequency is wrong you can use the ENABLE signal:

Note that I have not tested this since I generated the RGB selection signal using the circuit described in section 5.

5 An unified solution for horizontal frequency monitoring, RGB selection and adaptive polarity sync signal generation

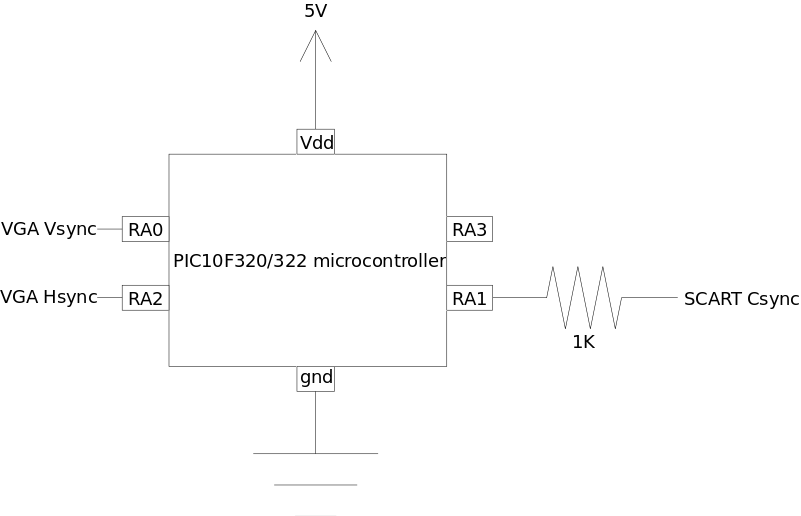

To finish, I proudly introduce my main contribution: a enhanced circuit to generate the composite sync signal. It uses a cheap PIC10F320/322 microcontroller featuring a configurable logic cell (CLC).

5.1 Pros

- It is the easiest to make since has only two components (the PIC and a resistor) and requires only 6 connections.

- It will automatically detect the polarity of the input sync signals and configure the CLC to generate the composite sync correctly.

- If you are using it to generate the composite sync signal of an old CRT monitor, you will not need any additional circuit to protect it from wrong input frequencies. The PIC monitors the input signal and set the composite sync to ground if the frequency of the horizontal sync signal is wrong or if the vertical sync signal does not change.

- With a few additional components it can also generate the RGB selection signal, the shutdown signal of the DC-DC converter (if used) and provide visual indication of the correctness of the input signals.

5.2 Cons

- You will need a way to flash the PIC with the code.

5.3 Code

You can download the compiled PIC code in hex format here and the C source code here.

5.4 Basic schematic

This is the basic circuit:

This will adjust to any sync polarity and will set the output to ground if the horizontal frequency is wrong or there is no activity in the vertical sync signal. As in the previous circuits, it is advisable to connect decoupling capacitors between the supply pins of the PIC to ensure it works properly. The manufacturer recommends two capacitors of 0.1μF and 0.01μF in parallel.

5.5 Enhanced schematic

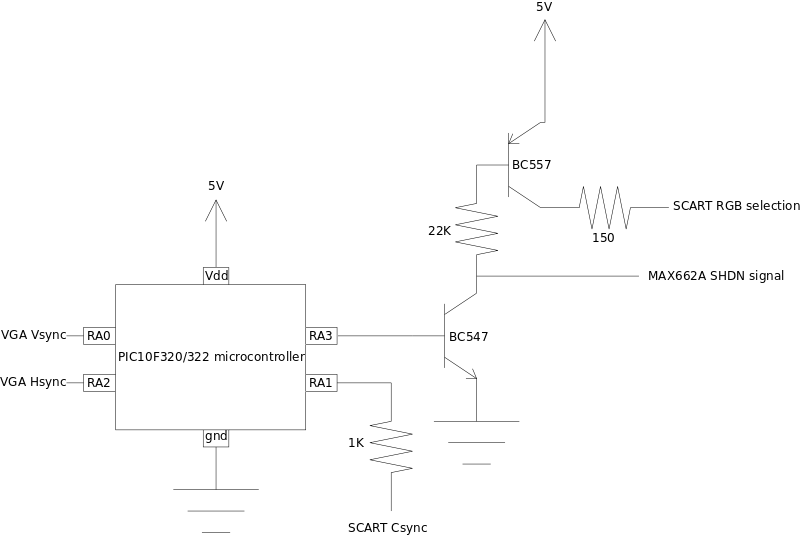

The PIC has only four I/O pins (RA0, RA1, RA2, RA3). The CLC can only use the pins RA0, RA1 and RA2 so I had to chose these pins for the sync signals. RA3 can be used to generate the RGB selection signal and control the DC-DC converter by using this circuit:

The lack of resistor between RA3 and the base of the NPN transistor is not a mistake: It turns out that RA3 is an input-only pin so I had to use this hack to turn it into an output. You can replace the 22KΩ resistor by another with a lower resistance in series with a LED to see if the frequency of the input signals are OK.

SCART VADER

SCART VADER