one of the biggest delays to getting terminal information to output is that it needs to work at separate times from the i2c bus and spi bus. spi bus is fast enough that this should not be an issue with outputting to lcd display. I want the terminal data to instantly show in terminal, so this may involve a ram buffer for the data to almost instantly show to terminal when i2c bus is idle.

there are two ways i may do this; 1 safely burst the i2c bus. this can only be done on read operations. so some checks need to be built in. do not do this with current setup. the library has been throttle limited to a max of 1mhz. but it might be able to burst to 2mhz in special situations. currently it is not a good idea and will require a lot of checks to make sure it works safely, but some status checks and verifying it is only this speed at read operations are needed. there is also the possibility of tuning the i2c frequency to optimum performance. when data can normally not be sent or received quickly enough the slave device can slow down the master device. this is if everything is in sync. at high clock rates this is unknown,

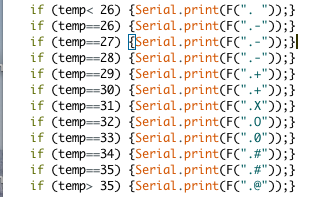

also there is a compressed buffer cache. normally reading output to terminal is low detail, the asci char generation is only 6 different char :

i have a way of fitting this data 3 bytes per 1 byte of cache. this is only for output to terminal. data is much faster internally. it also only uses 256 bytes of cache. it can be better because some number information is not processed for byte 1 and byte3. byte 2 will most likely have information similar to 1 +3

here is how i'll do it most likely

3bits is first byte value temp range

111|00|000

1st data

0 <26

1 >25 & <30

2 >29 & <31

3 >30 & <33

4 >32 & <36

5 >35

6&7 not used currently

000|00|111

3rd data

0 <26

1 >25 & <30

2 >29 & <31

3 >30 & <33

4 >32 & <36

5 >35

6&7 not used currently

000|11|000

2nd data

00 lowest value

01 1/2 of 1st and 1/2 of 3rd value

10 1/4 of 3rd value

11 highest value

I'm just looking at options to speed up serial terminal output. this may not even be needed after caching of i2c data. i2c is 1/8 the speed of when it will be cached...

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.