My first log ended with the word simple; scratch that. After a few rounds of refinement and some in-circuit validation many changes have been made. Before getting to that here are some of the challenges that make this seemingly simple idea complicated.

- TRIACs are susceptible to false turn-ons due to transients (high dv/dt) and can be difficult to turn off reliably depending on power factor and the associated dv/dt(c) & di/dt(c) (c=commutating). Understanding the load is very important.

- RC snubber networks are typically used to reduce dv/dt & di/dt in both commutating & transient situations. This design places opposing, out-of-phase voltages on each side of the TRIAC. These waveforms could also be of slightly different frequencies and peak-peak voltages. The snubber network, typically placed across MT1 & 2, would, in relative terms, have a high apparent power value and require larger wattage components. And while of small value, would also inject some harmonic energy back to the power source.

- Without a snubber network the TRIAC is much more susceptible to false turn-ons - catastrophic and potentially dangerous in this application.

- The circuit must be designed & tested with the type of load it will support. Reactive loads, particularly inductive, have poor power factors and hence high dv/dt(c). This design is intended primarily for resistive and SMPS loads < 100W.

- The control circuit must ensure that both TRIACs are not on at the same time and that there is a sufficient time gap between commutating events to ensure the TRIAC is off.

To elaborate on the last point, I labeled this project as a transfer switch but that is a bit of a misnomer. It does not function like those found in robust UPS' or other standby power systems. This is a stand-alone switch that has no control over the AC sources it is connected to and cannot synchronize voltage, frequency, and phase. Note also that if inductive loads will be controlled the di/dt(c) and peak current at turn-on could be very high - multiples of the load's rated starting current depending on where the core was on its B-H loop during the switching event.

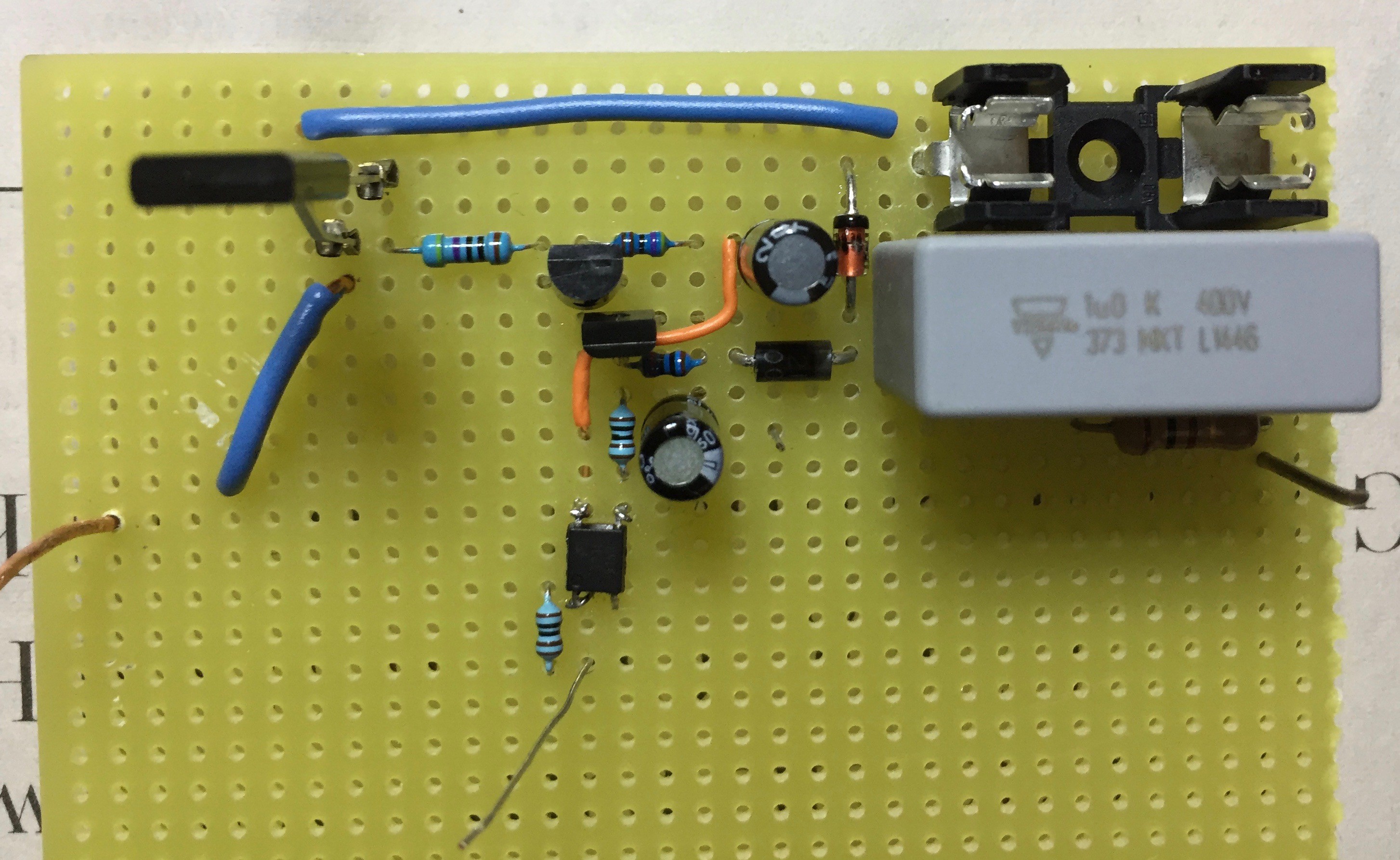

Taking the above into consideration I built the primary half of the circuit based on the original spice file. Note the fuse (500mA, fast): very important to avoid catastrophe. I started with a sensitive gate 2N6073B TRIAC from Littelfuse rated at 400VAC.

The optoisolator control circuit is in the bottom center and for testing is controlled with a switch & bench supply. Note the TRIAC (upper left) is mounted in a make-shift socket in anticipation of casualties.

No snubber was used and it was fairly easy to induce false turn-ons. While I couldn't add a conventional snubber I did add a 4mH inductor between the TRIAC MT2 pin and the output. The core is high permeability (TDK #B64290L0045X038, N=29, 20AWG) so it saturates at low current and doesn't materially interfere with the load's current waveform. What it does do is provide a small time delay at zero crossing and reduces the initial di/dt. This improved transient immunity but I was still able to induce false turn-ons.

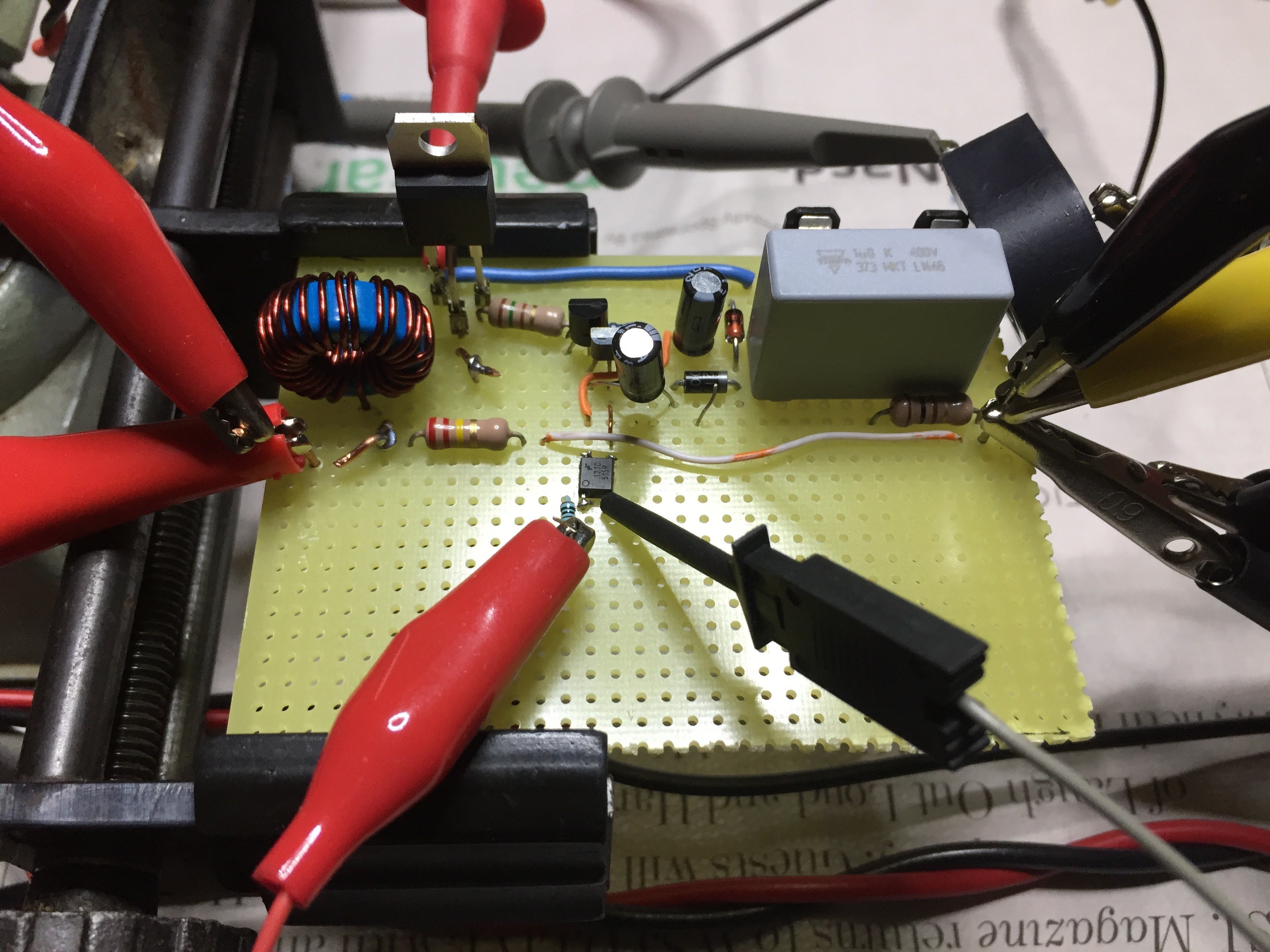

The 2N6073B was swapped for a T835T-8I from ST Electronics. This TRIAC is rated for 8A and 800VAC and requires a much higher trigger current of ~ 35mA. A huge benefit of a standard gate, higher voltage / current rated TRIAC is much better dv/dt immunity. This is because of the internal channel construction and the addition of resistors in the substrate to drain transient energy away from the gate.

While not perfect, it is rated for snubberless operation when operated within the confines of the data sheet. For comparison the T835T-8I's dv/dt(c) > 20V/uS @ 150C while the 2N6073B's maximum is 10V/uS @ 85C.

The picture above shows the T835T-8I installed for testing along with the output inductor. The 220K resistor shunts the output leakage to ground. This TRIAC tested good; I could not induce false turn-ons regardless of power cycle and transients (induced with an isolation transformer).

The most important static test of the concept required utility AC to the primary input and an auxiliary AC source across the output with the TRIAC off. The AC was cycled on each side independently and simultaneously to verify that, at least under static switching conditions, the TRIAC would not false trigger and that the control circuit didn't induce a spurious turn-on during power-up.

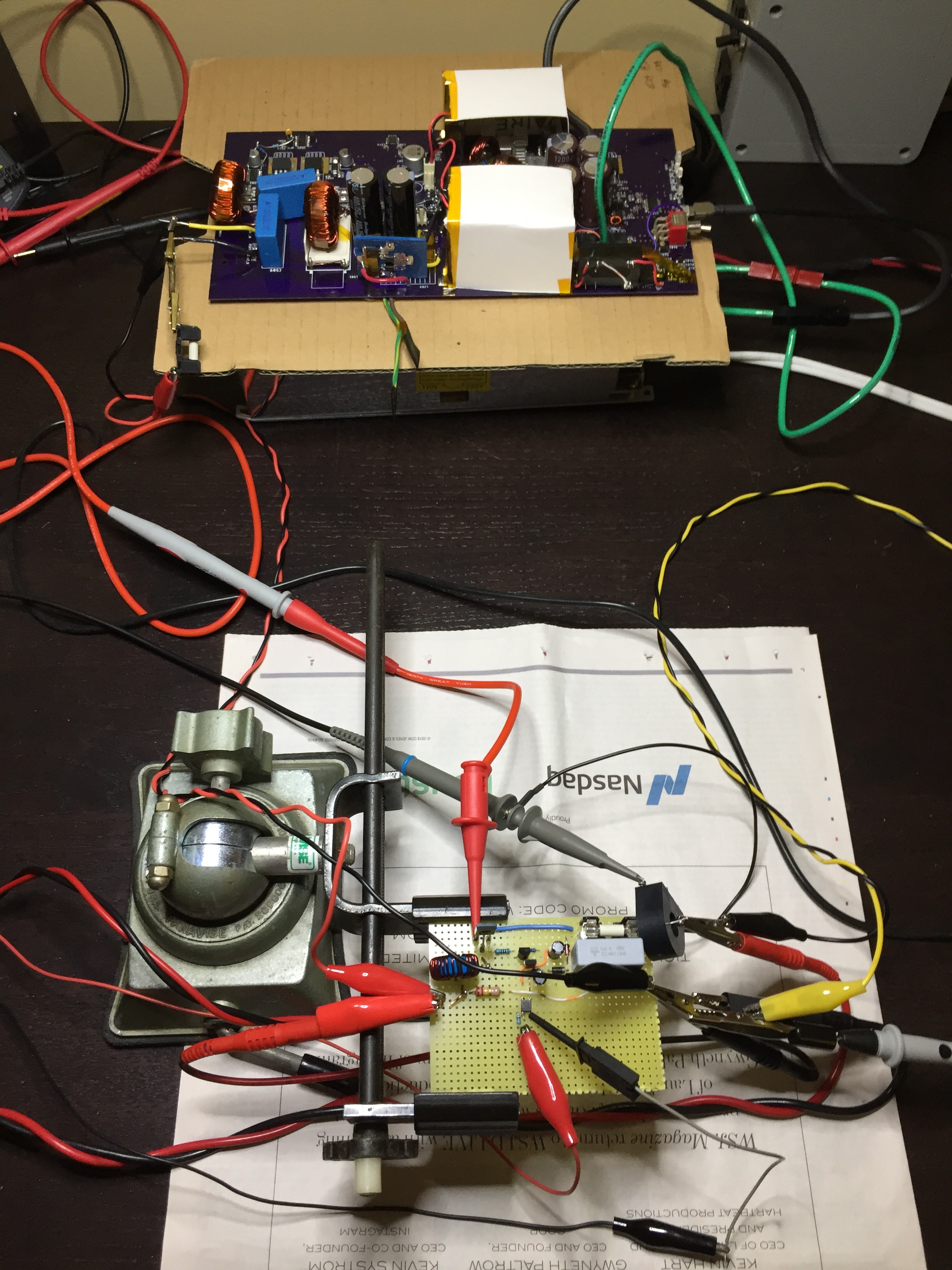

My other main project, the TS350, supplied AC to the output. The neutrals of both were tied together as common. Note the use of fuses at both AC inputs. This testing was successful too.

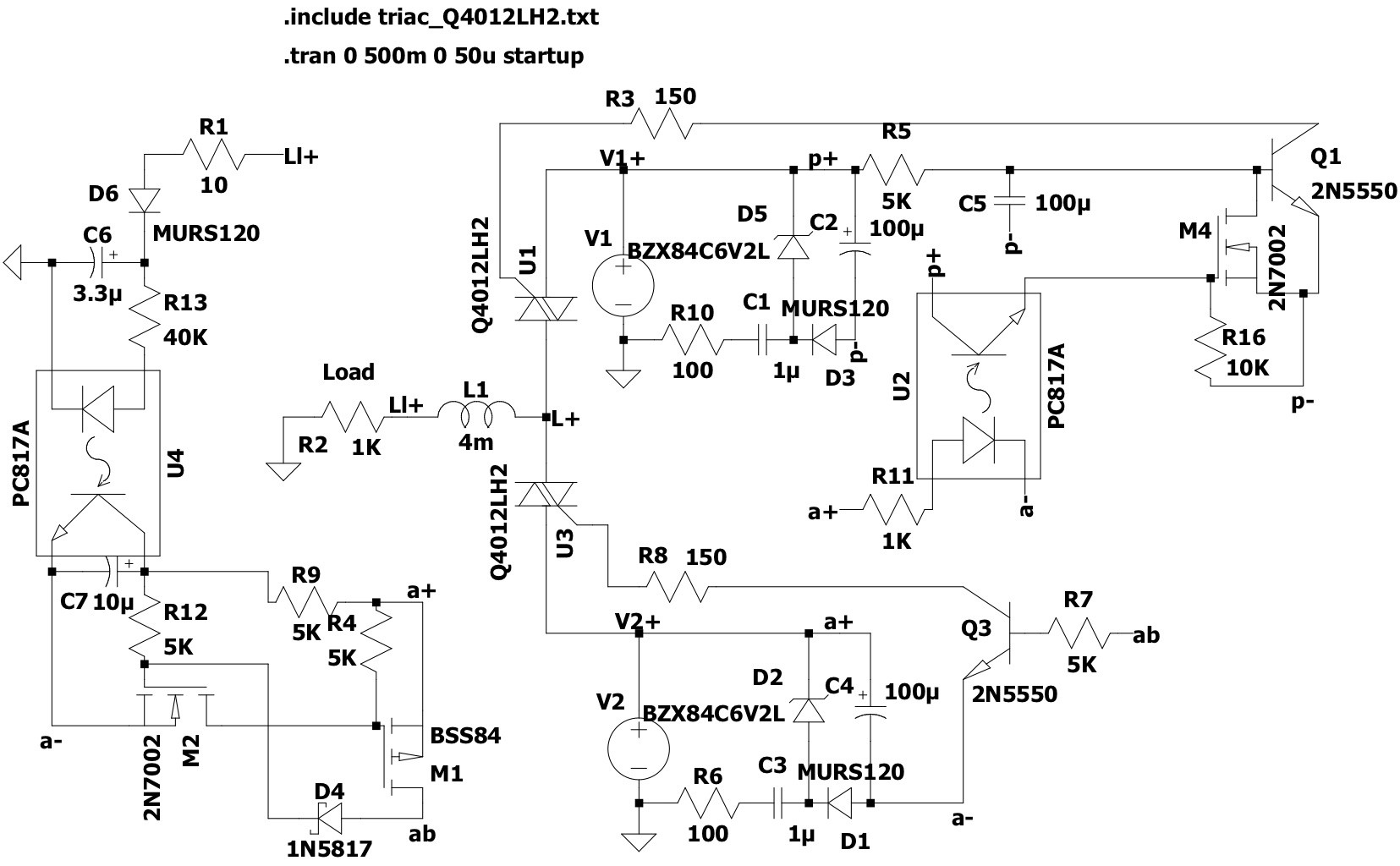

Here's the revised circuit which is also posted in the files section.

Power supplies are the same as original. The actual gate drive for both primary & auxiliary is simpler but the control logic is more complicated. I wasn't comfortable relying on RC timing circuits to control the switching mainly over concern for the TRIACs failure to commutate off properly. Instead I use the latch circuit on the left side of the schematic to manage switching. RC timing (C5) is still used to provide delays at power-up.

The latch works as follows. R1, D6, C6, and R13 form a simple half-wave dissipative supply powered by the output (LI+) and drives opto-isolator U4. R1 provides some reduction of in-rush current. The latch consists of U4's transistor, M1, M2, connected C-D-R components. The latch is powered by the auxiliary supply (a+) and drives Q3 (ab) to control the auxiliary gate.

When AC is applied to the auxiliary input the latch is powered. If the output is on, U4 will be biased and pull down the gate of M2 to keep it off. In turn R4 will apply a+ to M1's gate (a PFET) to keep it off.

Simultaneously, the auxiliary supply, a+, is applied to U2 which turns on M4 and removes the drive bias from Q1. TRIAC U1 should commutate off at the next zero current crossing. U4 turns off with the output which allows C7 to charge and when Vgs(th) is reached M2 begins turn-on, pulls down the gate of M1 turning it on. M1 drives Q3 which in turn commutates TRIAC U3 on. D4 maintains bias on M2 irrespective of the output voltage. The latch can only be reset by removing AC from the auxiliary input.

The time delay provided by C7 is necessary to ensure the primary TRIAC is fully off (think storage time with BJTs). If you try to reduce it be sure to verify experimentally using the intended loads.

Next I'll build the auxiliary half of the prototype and test. Perhaps overkill but I will use a second inductor so that each has a buffer against commutating events on the opposing one. At first I'll keep the primary & auxiliary outputs separate to safely evaluate timing.

So a simple SPDT solid-state switch has taken on a life of its own. It's a bit more complicated than I anticipated but it is straightforward. Unfortunately its not that efficient. Each of the capacitive supplies' true power is ~ 400mW but the apparent power is 4W RMS. U4 draws another ~ 1W when biased so the total true power is close to 2W RMS. Why didn't I just use a mechanical relay?

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.