The lasted developments seem to be successful !

v2.6 is progressing and I can already list not only the gates but their interconnections !

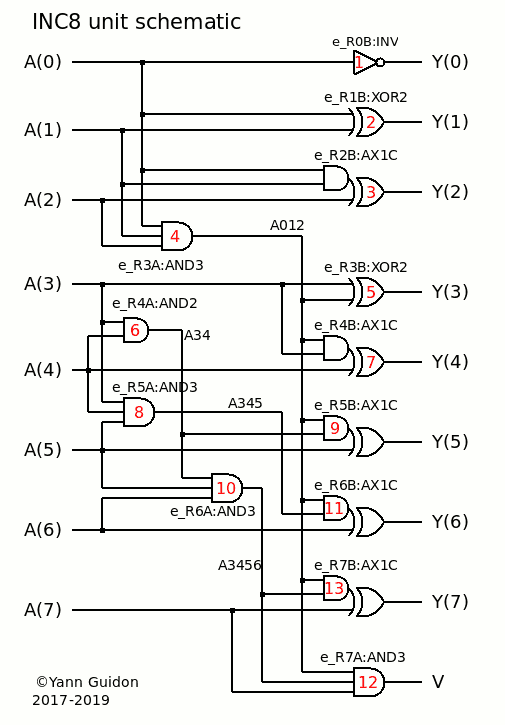

13x A3P gates found.

no exclusion input file to read.

Input vector : 8 bits, Output vector : 9 bits

Netlist : fixed

************ NETLIST ************

- Input #0 : fanout=4

1 : Gate #1(0) - inc8(tiles):e_r0b@inv(trace):lut2

2 : Gate #2(0) - inc8(tiles):e_r1b@xor2(trace):lut4

3 : Gate #3(0) - inc8(tiles):e_r2b@ax1c(trace):lut8

4 : Gate #4(0) - inc8(tiles):e_r3a@and3(trace):lut8

- Input #1 : fanout=3

1 : Gate #2(1) - inc8(tiles):e_r1b@xor2(trace):lut4

2 : Gate #3(1) - inc8(tiles):e_r2b@ax1c(trace):lut8

3 : Gate #4(1) - inc8(tiles):e_r3a@and3(trace):lut8

- Input #2 : fanout=2

1 : Gate #3(2) - inc8(tiles):e_r2b@ax1c(trace):lut8

2 : Gate #4(2) - inc8(tiles):e_r3a@and3(trace):lut8

- Input #3 : fanout=4

1 : Gate #5(0) - inc8(tiles):e_r3b@xor2(trace):lut4

2 : Gate #6(0) - inc8(tiles):e_r4a@and2(trace):lut4

3 : Gate #7(1) - inc8(tiles):e_r4b@ax1c(trace):lut8

4 : Gate #8(0) - inc8(tiles):e_r5a@and3(trace):lut8

- Input #4 : fanout=3

1 : Gate #6(1) - inc8(tiles):e_r4a@and2(trace):lut4

2 : Gate #7(2) - inc8(tiles):e_r4b@ax1c(trace):lut8

3 : Gate #8(1) - inc8(tiles):e_r5a@and3(trace):lut8

- Input #5 : fanout=3

1 : Gate #9(2) - inc8(tiles):e_r5b@ax1c(trace):lut8

2 : Gate #10(1) - inc8(tiles):e_r6a@and3(trace):lut8

3 : Gate #8(2) - inc8(tiles):e_r5a@and3(trace):lut8

- Input #6 : fanout=2

1 : Gate #11(2) - inc8(tiles):e_r6b@ax1c(trace):lut8

2 : Gate #10(2) - inc8(tiles):e_r6a@and3(trace):lut8

- Input #7 : fanout=2

1 : Gate #12(2) - inc8(tiles):e_r7a@and3(trace):lut8

2 : Gate #13(2) - inc8(tiles):e_r7b@ax1c(trace):lut8

- Gate #1 : fanout=1 Depth= LUT="10" - inc8(tiles):e_r0b@inv(trace):lut2

1 : Output #0

- Gate #2 : fanout=1 Depth= LUT="0110" - inc8(tiles):e_r1b@xor2(trace):lut4

1 : Output #1

- Gate #3 : fanout=1 Depth= LUT="01010110" - inc8(tiles):e_r2b@ax1c(trace):lut8

1 : Output #2

- Gate #4 : fanout=6 Depth= LUT="00000001" - inc8(tiles):e_r3a@and3(trace):lut8

1 : Gate #5(1) - inc8(tiles):e_r3b@xor2(trace):lut4

2 : Gate #7(0) - inc8(tiles):e_r4b@ax1c(trace):lut8

3 : Gate #9(0) - inc8(tiles):e_r5b@ax1c(trace):lut8

4 : Gate #11(0) - inc8(tiles):e_r6b@ax1c(trace):lut8

5 : Gate #12(0) - inc8(tiles):e_r7a@and3(trace):lut8

6 : Gate #13(0) - inc8(tiles):e_r7b@ax1c(trace):lut8

- Gate #5 : fanout=1 Depth= LUT="0110" - inc8(tiles):e_r3b@xor2(trace):lut4

1 : Output #3

- Gate #6 : fanout=2 Depth= LUT="0001" - inc8(tiles):e_r4a@and2(trace):lut4

1 : Gate #10(0) - inc8(tiles):e_r6a@and3(trace):lut8

2 : Gate #9(1) - inc8(tiles):e_r5b@ax1c(trace):lut8

- Gate #7 : fanout=1 Depth= LUT="01010110" - inc8(tiles):e_r4b@ax1c(trace):lut8

1 : Output #4

- Gate #8 : fanout=1 Depth= LUT="00000001" - inc8(tiles):e_r5a@and3(trace):lut8

1 : Gate #11(1) - inc8(tiles):e_r6b@ax1c(trace):lut8

- Gate #9 : fanout=1 Depth= LUT="01010110" - inc8(tiles):e_r5b@ax1c(trace):lut8

1 : Output #5

- Gate #10 : fanout=2 Depth= LUT="00000001" - inc8(tiles):e_r6a@and3(trace):lut8

1 : Gate #12(1) - inc8(tiles):e_r7a@and3(trace):lut8

2 : Gate #13(1) - inc8(tiles):e_r7b@ax1c(trace):lut8

- Gate #11 : fanout=1 Depth= LUT="01010110" - inc8(tiles):e_r6b@ax1c(trace):lut8

1 : Output #6

- Gate #12 : fanout=1 Depth= LUT="00000001" - inc8(tiles):e_r7a@and3(trace):lut8

1 : Output #8

- Gate #13 : fanout=1 Depth= LUT="01010110" - inc8(tiles):e_r7b@ax1c(trace):lut8

1 : Output #7

************ END OF NETLIST ************

This is the netlist extracted from the INC8 unit and it's getting better and better. It matches well with the schematic :

I'm polishing things and I should add a few things :

- histogram of the fanouts...

- find a way to activate/trigger a given LUT entry

- "compile" the "depth" and check for loops or disconnected stuff

- ...

The latest update has a few enhancements and the ALU8 passes the netlist extractor :-)

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.