No it's not another Doctor Who fanfic ;-)

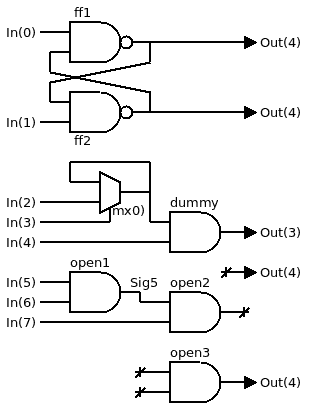

The logic depth analysis detects logic loops in digital netlists and this is a good safety net because otherwise, it couldn't tell the depth anyway. This is explained in the log Zombies in v2.6 with the classic examples of a dual-NOR2 flip-flop and a MUX-based latch (among others) :

The analyser can detect the incoherent logical depth but can't tell if a logical loop is either a latch or an oscillator (or both ?) so it's safest to just exit with an error.

But this is not enough : not all digital circuits are pure boolean networks and loops happen in a way or another. As described in the log 127. A tale of Flip-Flops, I also need to handle DFF, RS FF and transparent latches. I also describe a model for dealing with them all.

DFFs are quite easy to model : just consider its inputs and outputs as ports, because the effect is not on the current clock cycle.

But I also need Set/Reset flip-flops and I have defined a table of "macros" (which will then be substituted with the real gates) as well as a strategy to allow the analysis.

| Precedence | Set level | Reset level | Macro name | Mapped to |

| Set | 0 | 0 | S0R0 | AO1A |

| Set | 0 | 1 | S0R1 | AO1C |

| Set | 1 | 0 | S1R0 | AO1, AON21 |

| Set | 1 | 1 | S1R1 | AO1B, DLI1P1C1, AON21B |

| Reset | 0 | 0 | R0S0 | OA1A |

| Reset | 0 | 1 | R1S0 | OA1C |

| Reset | 1 | 0 | R0S1 | OA1, OAN21 |

| Reset | 1 | 1 | R1S1 | OA1B, DLN1P1C1, OAN21B |

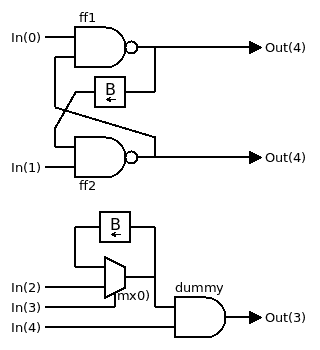

Let's add to this a new "virtual component" : backwards is a "time machine" that sends the value of one net to another identical net but with a different logic depth. The "simple" definition is just a wire that will be simulated as such, but the analysis version breaks the temporal causality that defines the loop (while also preserving the fanout so this is not a buffer).

I had to invent a symbol so I chose a B with a leftwards arrow... Here is the "weird circuit" with the appropriate new symbol :

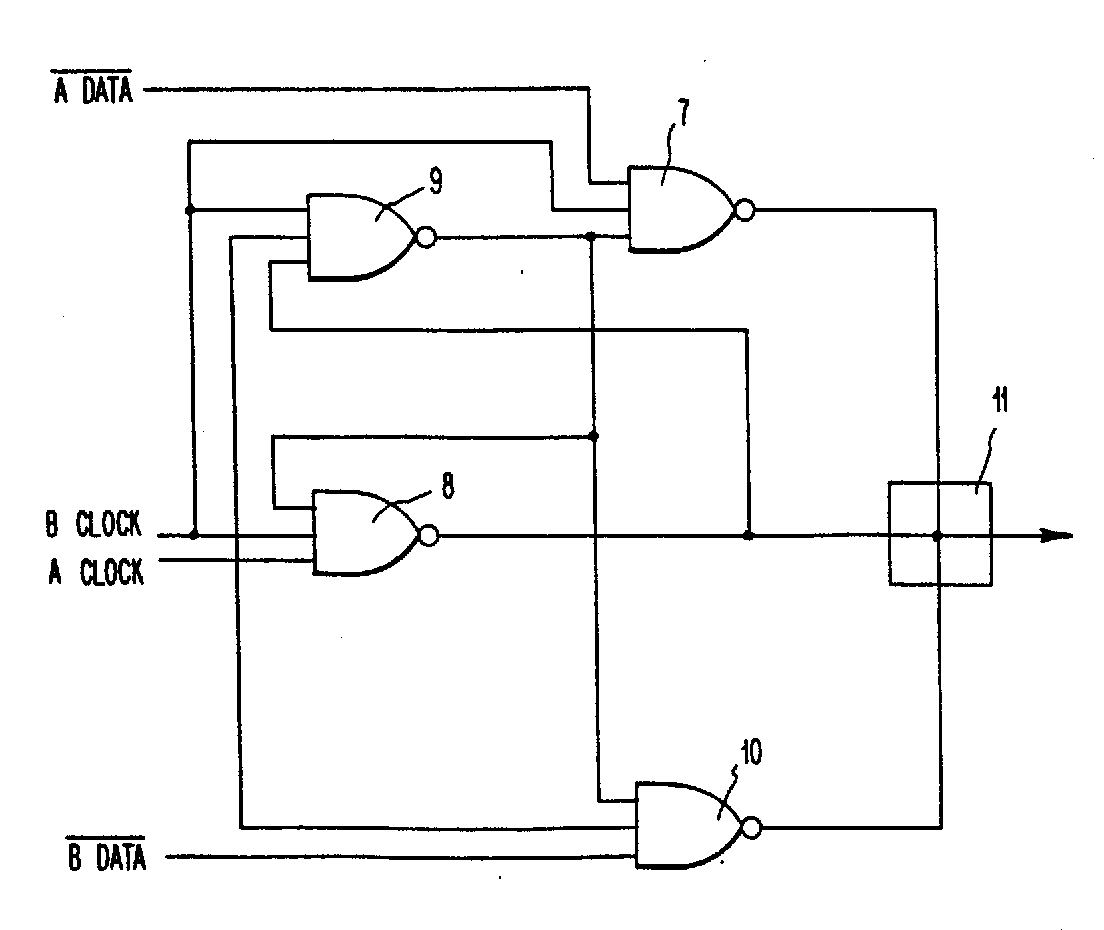

This new component is a first little step toward a more extensive redesign that will allow the other types of sequential gates to be analysed, such as this circuit (from an old IBM european patent EP0092663A2 from 1983).

(there would be 2 "backwards" meta-components)

I have added the two files SRFF_simple.vhdl and SRFF_PA3.vhdl to the A3P library. It shouldn't belong there, strictly, but I have no other place for it (yet).

.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Sigh...

The first version swapped R0S1 and R1S0...

Are you sure? yes | no