A while ago I bought some MC68020RC12s, and I recently decided it was time to do something with them, so I made a little adapter that allows the 020 to plug into the 64-pin DIL socket used by the MC68010 on the rosco_m68k. Of course this limits the 020 to 24-bit addressing and 16-bit data, but seemed a fun project and a good way to get started with integrating the 020 in preparation for the future.

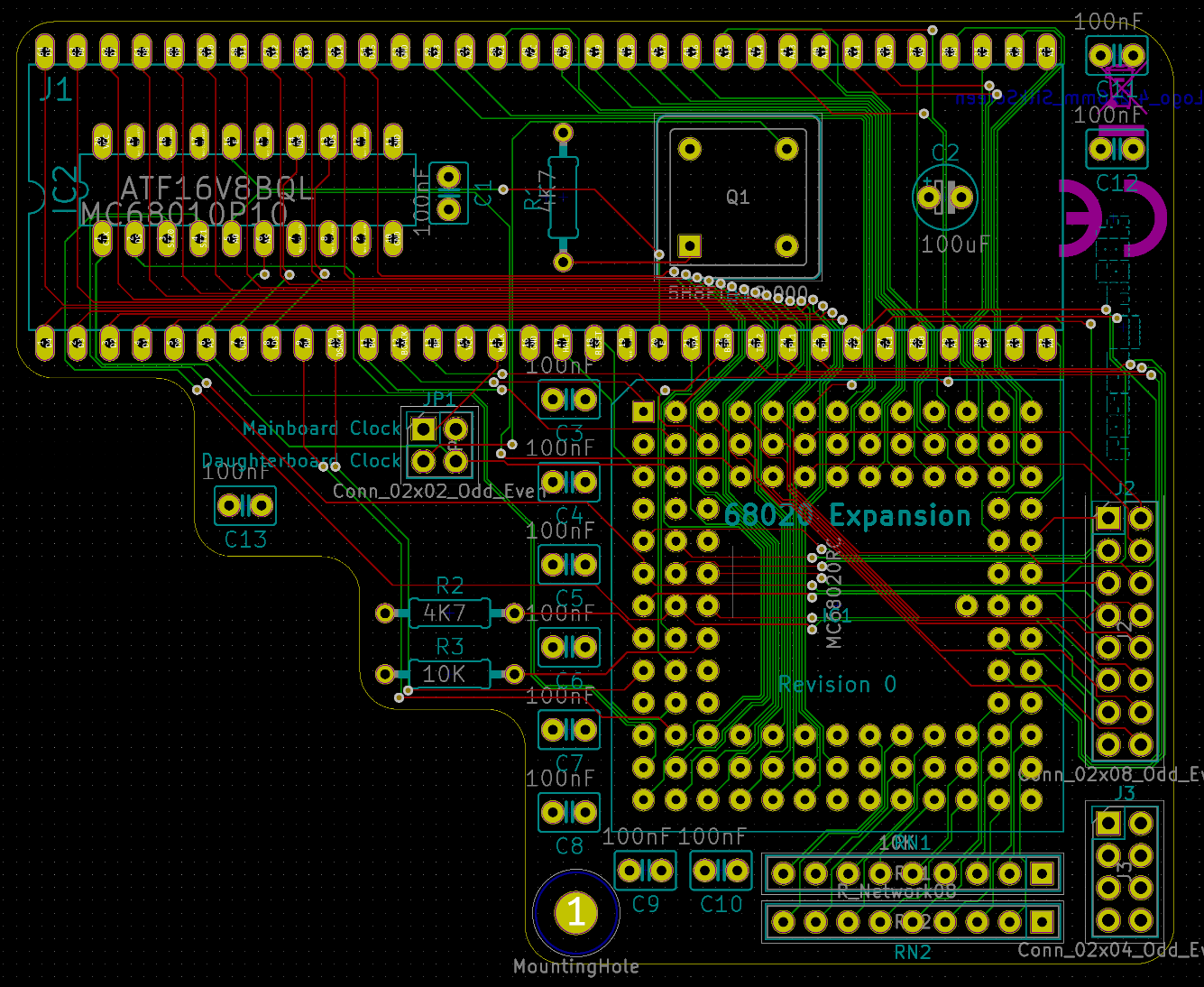

The idea is basically to connect up the 020 to the mainboard bus, plus allow it to have it's own clock. There's a little bit of glue logic translation done by an ATF16V8BQL on the board. The layout looks like this:

The design isn't ready for prime-time yet, but I had a few prototypes made, and it works perfectly on the revision 1 board. There's an issue with DTACK generation on the revision 1.2 (which isn't new, we've known about it for a while but I've put off fixing it as it was "good enough" - until now).

When plugged into the main board (with some spacers on the headers going into the CPU socket to give some vertical separation from the RAM/ROM chips) it looks like this:

Even with the 16-bit bus (and with a relatively-slow 12MHz 020), this is already showing an impressive turn of speed in benchmarks. The 10MHz 010 dhrystone results were:

Even with the 16-bit bus (and with a relatively-slow 12MHz 020), this is already showing an impressive turn of speed in benchmarks. The 10MHz 010 dhrystone results were:

rosco_m68k 68010-10Mhz ROM gcc-7.5.0 - 1086 (-O1)

rosco_m68k 68010-10Mhz ROM gcc-7.5.0 - 1086 (-O1)

While the 020 gives:

rosco_m68k 68020-12Mhz ROM gcc-7.5.0 - 2604 (-O1) rosco_m68k 68020-12Mhz ROM gcc-10.2.0 - 2860 (-O1) rosco_m68k 68020-12Mhz ROM gcc-10.2.0 - 2941 (-O1 -mtune=68020)

(The score is the figure in the right column, for a fair comparison both GCC 7.5.0 (which we were using at the time we last benchmarked the 010) and the current GCC 10.2.0 have been tested.

As usual, the design files, PLD code and gerbers can be found in the hardware projects repository in GitHub: https://github.com/rosco-m68k/hardware-projects/tree/master/r1_020_expansion

Ross Bamford

Ross Bamford

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.