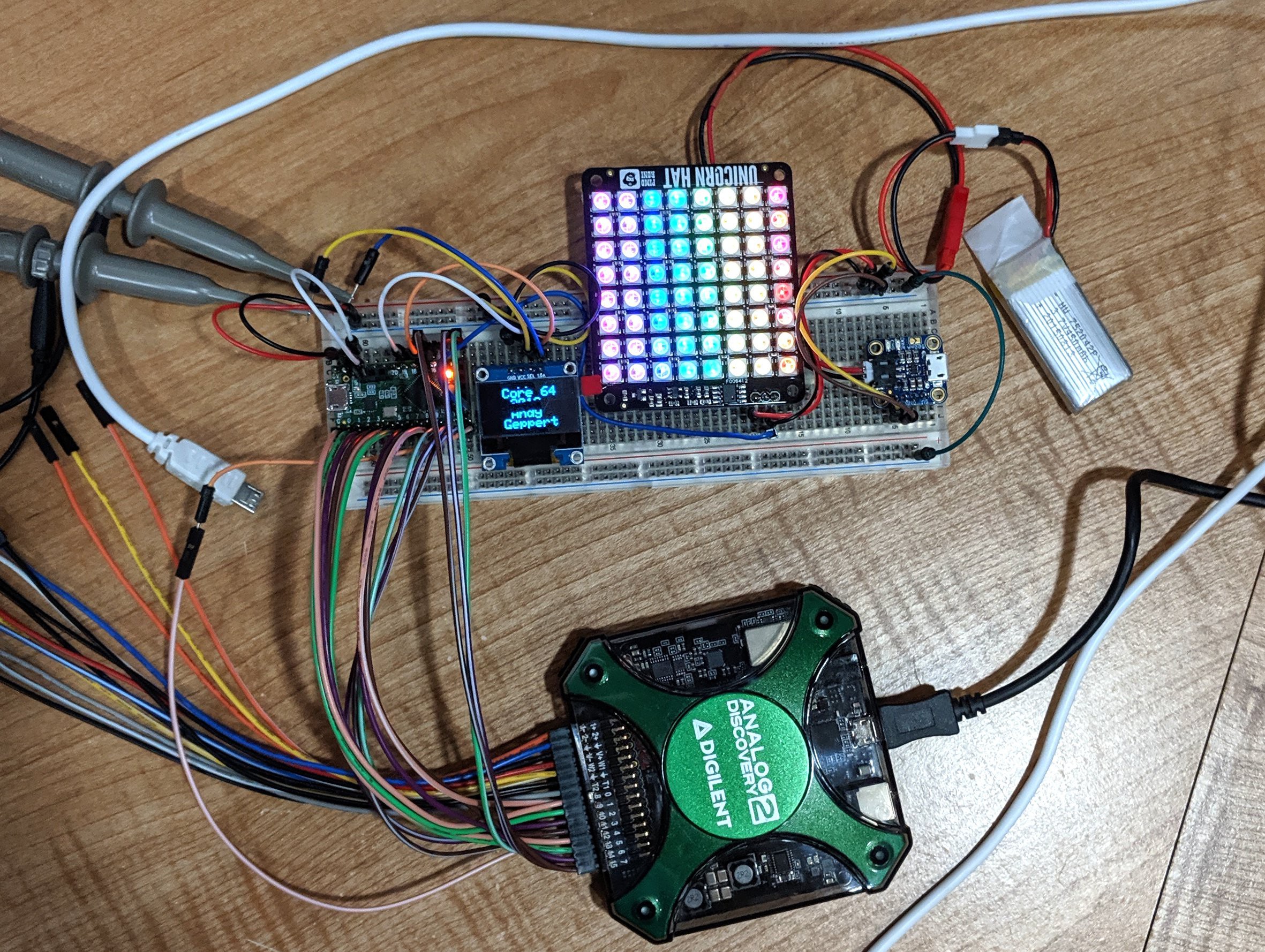

In order to make sure I have a workable hardware solution, I'm pulling together the various components I intend to use to make sure there is enough IO and that it maps out as I think it will to the Teensy LC pins. The source code on Github has been updated to reflect the state of the project now.

The important parts of this hardware testing are:

- Will it all run from a single cell LiPo since that is the lowest voltage I intend to use? Yes.

- Since I plan to use discrete IO on the Teensy LC to directly drive the 20+ transistors needed for 64 cores, are there enough pins without conflicts? Yes, although some pins will be used for more than one function to keep a few IO pins open. The shared pins will be: I2C bus, LED Array.

- The LED Array runs well on GPIO 17 through the buffered output with a 1S LiPo. The Unicorn Hat looks like a great option to use directly, as is.

- The OLED screen is for testing the I2C bus, which I intend to use for some hall sensors and general expansion.

- As shown above, the components are drawing about 70 mA. The LED matrix brightness is set as low as it can go. The cores are not running, but the current pulse is expected to be about 300-400 mA, and will be handled with a capacitor to make sure the system doesn't brownout.

TO DO NEXT:

Connect and drive some cores through Jussi's 4x8 shield to ensure adequate power sourcing. Then get going on the circuit and PCB prototype in KiCad!

Andy Geppert

Andy Geppert

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.