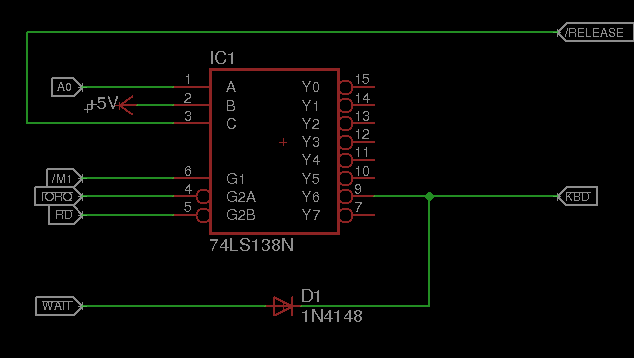

That's a possibility for a /KBD and /WAIT signal generator.

Everytime the Z80 perform a READ at IO address xxxxxxx0 and the pin /RELEASE coming from AVR is at HIGH state, the output Y6 Will go LOW and will generate the /KBD signal to interrupt the AVR and also will signal Z80 to WAIT and the AVR will have more time to attend the external interrupt.

Afther the correct data have been put on KB0-KB4 lines the AVR can drop the /RELEASE line for a period of time equivalent to the end of "IN (C),A" iinstruction (1us will do the job) and then return the /RELEASE line back to high level.

I hope this mechanism can work without a companion flip flop, like in the external version.

danjovic

danjovic

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.