During work on the C compiler it appeared that the instruction set had some problems. Compiling was possible, but sometimes resulted in code that was longer than optimal. (Of course the lack of AND, OR and XOR also can give longer code, but that was accepted from the beginning and I won't change that. Not now :) ).

The main problems were:

- When storing a register to memory, the contents of that register changes

- Move from one data register to another one is not possible.

- Instructions with 3 operands exist, but placed strong restrictions on the involved registers

- Compare instructions don't exist. An ADD is used instead, with unwanted effect that the sum is written to a register.

Of course the change must be small, because I will also have to change the hardware prototype and I don't want a lot of rewiring.

CHANGES

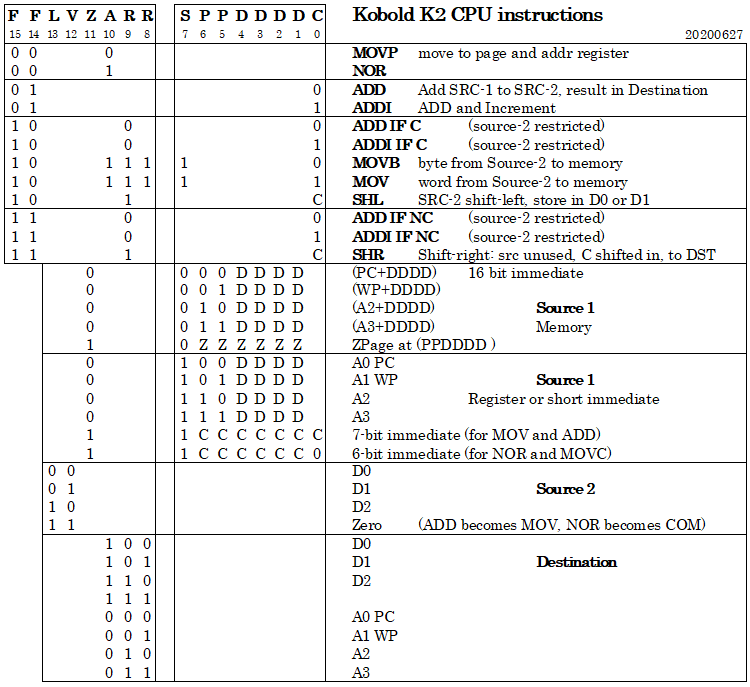

The main change is the introduction of many 3-operand instructions. The second operand is always a register, and when this is register D3, this transforms a ADD in a MOV because D3 is now always zero. A new RISK feature !

The other problems were also addressed. Of course new restrictions appear: Register D3 can not be used to store a value. The number of Z-page addresses goes from 128 to 64, and the result of a shift instruction always goes to D2.

The new features:

- When storing a register to memory, the contents of the register stays the same.

- All register-to-register moves are possible.

- Many 3-operand instructions available.

- A CMP instruction is introduced (it is an ADD instruction, but only writes CY and doesn't change a register.

Some other new instructions, that were not in the problem list but are quite useful:

- A memory position can be cleared without having to load a register with zero (The CLR instruction stores the always-zero D3)

- Many register-to-register instructions can be conditional (executed when CY is 0 or 1).

- Many MOV and ADD instructions (also 3-operand versions) can be conditional

The new set needs one extra AND gate. That's an extra IC. Perhaps a few of the other gates can also get a useful function....

SO HERE IT IS

TODO

- change the assembler

- change the manual of the assembler

- change the simulator

- change the C compiler

- change the hardware

[ add 2 weeks of changes and debugging ]

DISILLUSIONMENT

After more than two weeks, I could not get this to work. Many opcodes changed, requiring changes at several places. The automatic jump-size detection and associated complexities did not do what I wanted them to do: the programs would not run well on the simulator, so I didn't even dare to change the hardware and test on that.

So I gave up on that.

Then came a few days that I worked on a simpler form of these changes. I got the assembler and simulator working, but after modifying the hardware I got non-logical behaviour of initialized global variables. Difficult to debug. Or build a debugging tool first ?

Yesterday I decided that it was not worth the trouble. I rolled back all changes from this log.

Except one change: there will now only be 64 zpage variables (instead of 128). Like 64K, 64 globals should be enough for everybody. This leaves us one bit (Instruction bit 7) totally free for later use. So, only 50% of the instruction space is used !

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.