What is done?

- I/O space design is designed

- Memory space design is designed

- USB, I2C and Serial port peripherals are included

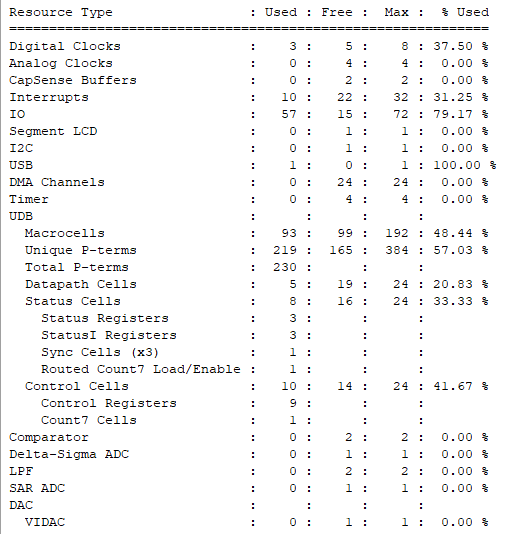

The resources of this consume about half of the programmable logic in the PSoC.

Still to do

- Add two address bits for SRAMA[12..11]. This is an enhancement out of the memory mapper implementation and allows for minimum 2KB block size mapping.

- Interrupt controller - generate interrupts to the Z80. That should be as simple as the PSoC setting the NT* line to the Z80 and the bit would be cleared by an interrupt acknowledge cycle from the Z80.

- It would be fun to add connections to the DAC for sound generation. This could be controlled by the PWM in the PSoC.

I am not yet I/O limited but getting there soon. I could free up the BREQ* and BG* lines since I'm not planning on using that functionality.

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.