I've spent quite a few hours this weekend here

It's starting to look a lot like my bedroom when I was a kid, not sure if that's good or bad though... :D

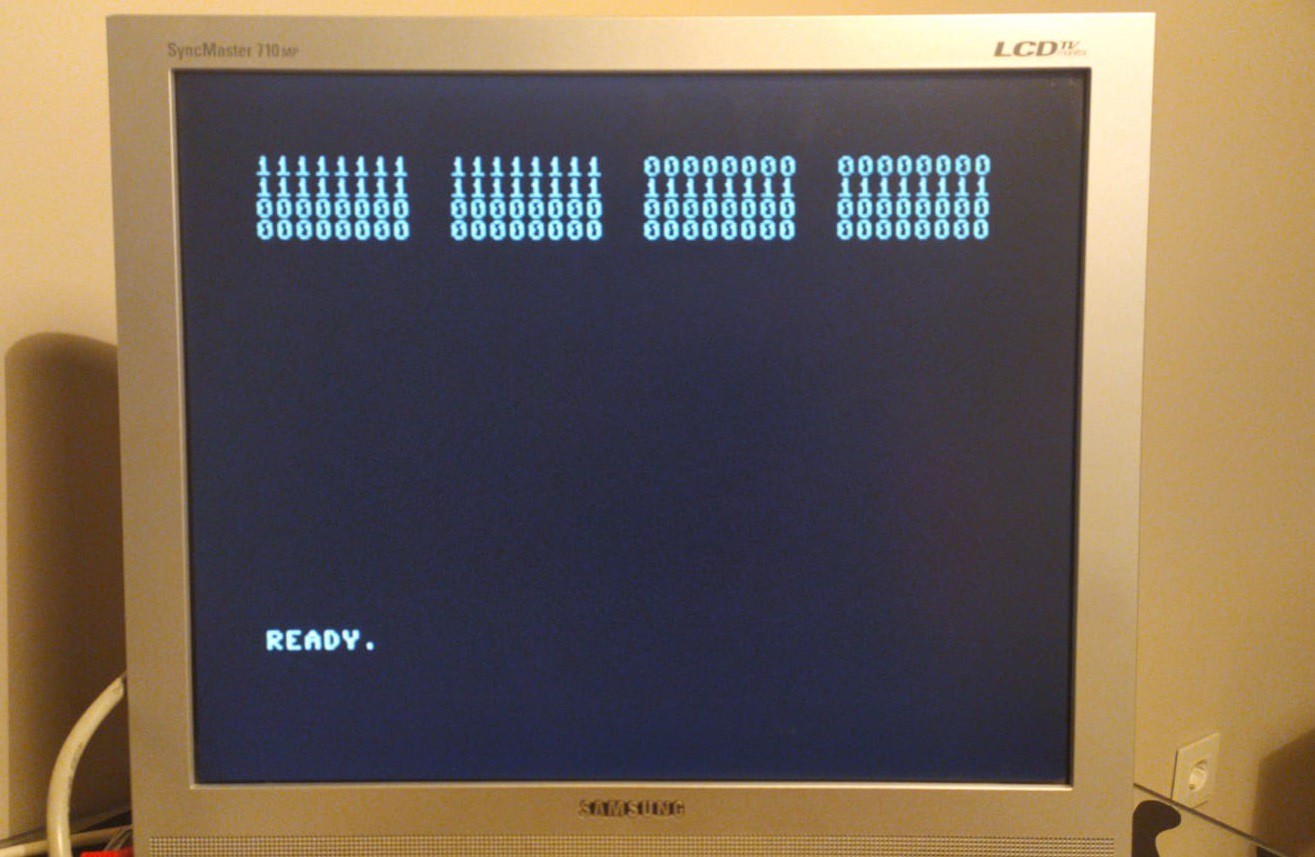

Using a small piece of assembly that took me 2 hours to complete (I've got so rusty)

I've been able to try plenty of stuff. There are some things remaining that will need some heavy use of my logic analyzer, as timing's crucial.

The good news so far :

- Starting values. Timers' latches should be set to 1, control register to 0. Big facepalm here, as I completely messed up the schematics, a (very much) needed inverter is missing. As a consequence, Timers' latches are perpetually set to 1. Some PCB hacking has been done and, now they initialize with rubbish, but at least I can write to them. An easy fix for rev 2. Control registers initialize OK

- PB7 and PB6 override. Setting the bit in the control register forces PB6 and PB7 as outputs.

- Timer reloading from latches. Works fine, whenever a write to the high byte with timer is stopped, whenever FORCELOAD is written with a 1 (which is stored nowhere), or whenever there's and underflow

- Timer output on PB6 and 7. TIMERB toggle output works. Pulse output requires the logic analyzer to check. TIMERA output is completely missing. Circuits are the same for both timers, so could be caused by a bad solder

- Timer B won't count Timer A underflows. Could be related to the above issue

- One shot mode. It works, timer counts down until the overflow happens, Then relatches the value.... but then it ticks once more before stopping. Same for both timers.

The untested bits:

- Pulse output.

- CNT pulses counting

- Different overflow behavior counting PHI2 vs CNT (4-3-2-1-4-4-3-2 vs 4-3-2-1-0-4-3-2-1-0)

And the know issues:

- TIMERA underflow seems to fail. Could be a bad solder

- START bit gets set to 1 on its own sometimes. Same for both TIMERS.

- Adittional tick in One Shot Mode. I think this is caused by the 2 DFF feeding the clock to the Timer. When Timer stops, there more clocks in the queue. I probably need to clear one of them when the underflow is reached.

All in all... I'd say it's a 7/10 score so far. START bit has me scratching heavily my head... but I think I should better sleep on it. I've had no ideas about what's causing this so far.

Cheers!

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.