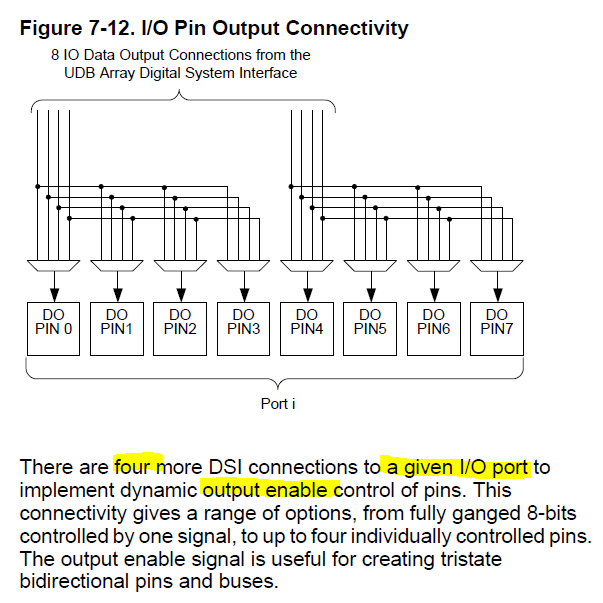

There's an interesting limit on the PSoC for output enables. Each 8-bit port can only have two output enables.

This makes creating a general purpose port difficult. Unless the pin is set to be open collector and driven low. With a pullup on the input. That could work. There would need to be a gate on the output which effectively disables driving the line low.

In order to check the pin assignments, I created a PSoC design file with all of the ports set up as GPIO lines. As noted above there are only 2 Output enables per block so this did limit the general case of I/O pin direction control on individual pins.

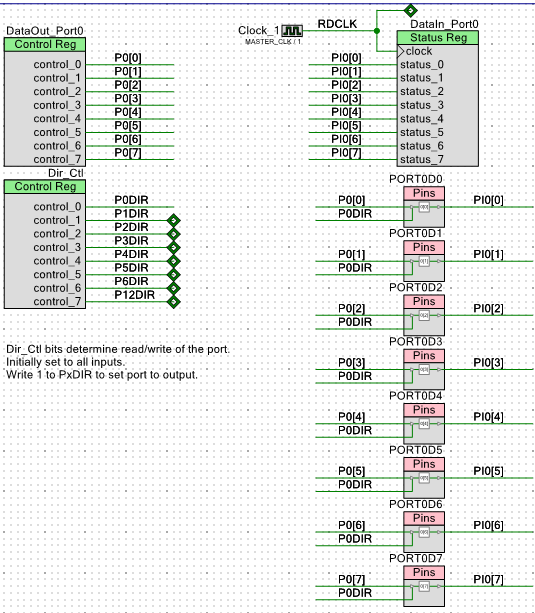

Here's what one 8-bit port looks like:

The Dir_Ctrl register sets the direction of the GPIO pins. The register powers up with all outputs at 0 so this means all of the I/O pins are input pins at power up.

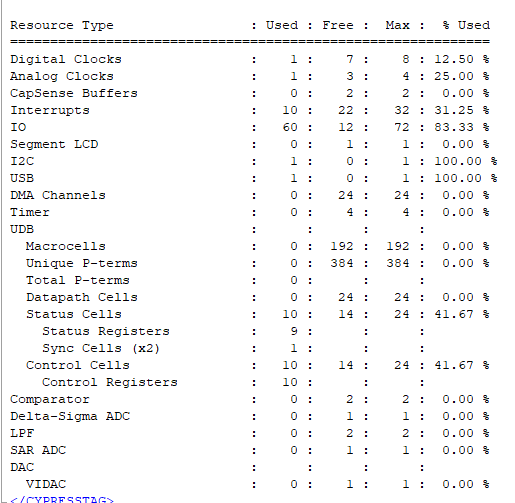

I made ports for all of the pins. This used the following resources:

This is less than half the Control and Status registers in the PSoC. Of course, some of these ports will be set up for specific functions (UARTs, etc).

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.