The first version of the Nits Processor is now finished. It is turing complete with a very basic set of instructions, it is possible to upload a program and run it, it can display a result on the 7-segment display.

Here are a few photos.

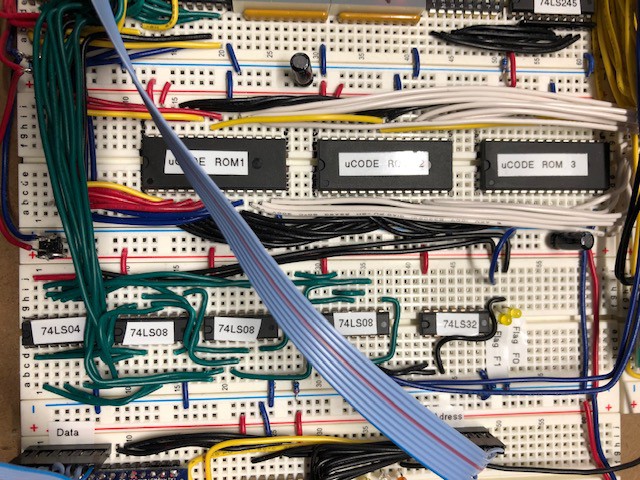

The instruction decoder (3 EEPROMS for 17 signals and a set of gates to decode the flags):

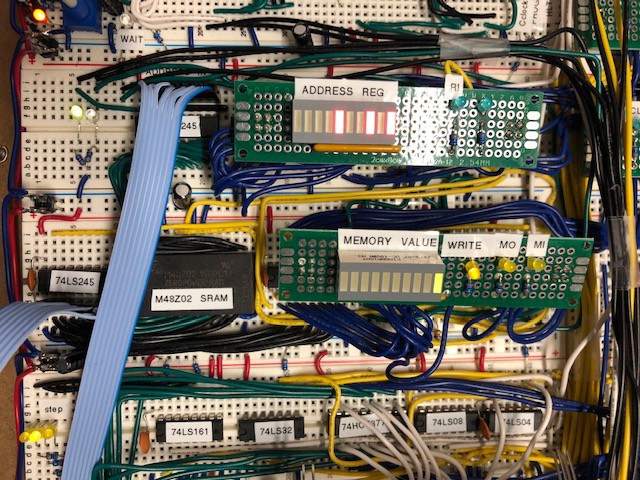

The memory (256 bytes stored in Non Volatile Static RAM, with the Address Register, the memory value display).

The two flat cables come from the memory loader module (Arduino based). One is the Address bus and one is the data bus. They are used in PROG mode to upload the program to the memory.

It is now time to think about the next steps. What are the current limitations and how can it be improved.

Improvements can be of 3 sorts:

- Improve the instrution set

- Improve the architecture

- Improve the build

Improve the instruction set

The instruction set is very limited and really needs to be expanded to provide usable capabilities. For instance:

- Add basic logic functions (And, Or, Not, Exclusive or)

- Add shift functions (Shift, Shift Circular, Shift with carry)

- Add compare functions (zero, equal, greater than)

- Add Push and Pop capability (requires a dedicated stack pointer register)

- Add Call and Return

- Add bit management (test flags, store flags, bit operations)

Improve the architecture

With only 2 registers, the lack of stack pointer and only 256 bytes of memory for both data and program, the current archietcture can really be improved:

- Expand address bus to 16 bit (hence 64 Kbytes of memory). However this requires many changes because now the address bus can be double the size of the databus and ALU creating a challenge when computing addresses

- Expand the number of registers, at least to 4 General Purpuse Registers

- Separate memory from Input-Output. This will provide double the addressing capability

- Add a way to interact with the system, for instance with a proper serial interface

- add a ROM with basic functions including initial setup and serial management

- add a stack pointer and index registers for points in memory

- add interupt management (is required for serial interface)

- expand the ALU capabilities

Improve the buid

In its current form (build on breadboards), the CPU works well at 1 Mhz, however, when putting a 4 Mhz oscilator, it breaks. And this is normal considering the capacitance of the breadboard and how the cables are set up.

It would therefore be interresting to improve on the design with:

- a PCB backplane to handle all the busses and the clocks with proper connectors (I'm investigating the 96pint DIN41612 connector)

- PCB modules for very stable elements such as registers, clock

- Keep the breadboards for test modules and modules that keep beeing improved (ALU, IO)

- improve on test modules

Ced

Ced

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.