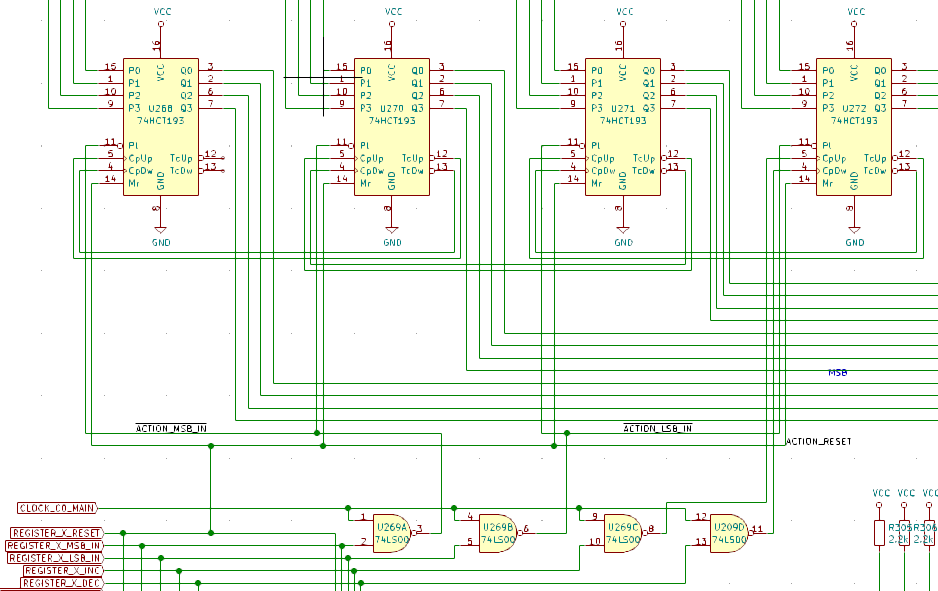

Still working with the GPAR, the General Purpose Address Register. This design includes 4 chained 74HCT193 up/down counters. Each one handles 4 bits and the Adress Register can handle 16-bits in total.

For some operations, the four 193 will work in parrallel, such as the RESET function, or the parrallel load.

But, when using the INCrement or DECrement function, each one has to wait until the previous one is done computing to see if it needs, in turn, to increment or decrement. There is therefore an extended propagation delay for these functions.

Using a 100Mhz digital Logic Analyzer, we are going to measure the delay when using the increment or decrement function. Note that this logic analyser can only sample the signal at 100Mhz, therefore the maximum speed is one sample per 10ns. So the results are not very precise but it can illustrate what is going on.

For this, we plugged the GPAR to a 4Mhz clock, set the DEC function to permanent activation, therefore, the GPAR is decrementing at the speed of the clock, 4 million times per second.

Schematic of the GPAR

The DEC function goes first through a NAND (74HCT00) gate to synchronize with the clock then to the CpDw pin of the first 74HCT193, then each 193 is chained using the special purpose output TcUp and TcDw.

Step 1 - Delay at the NAND gate

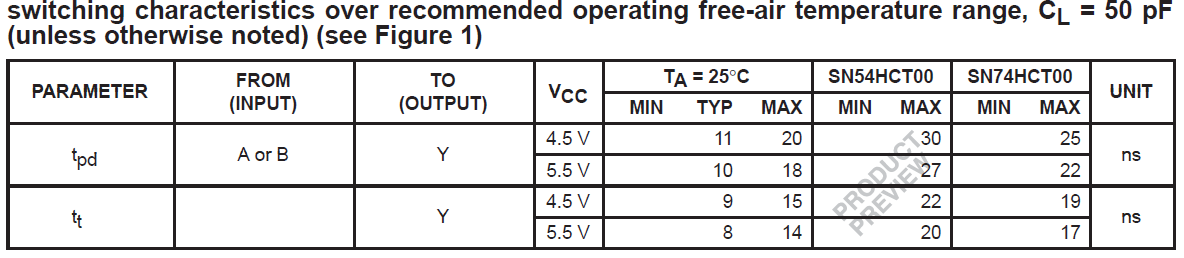

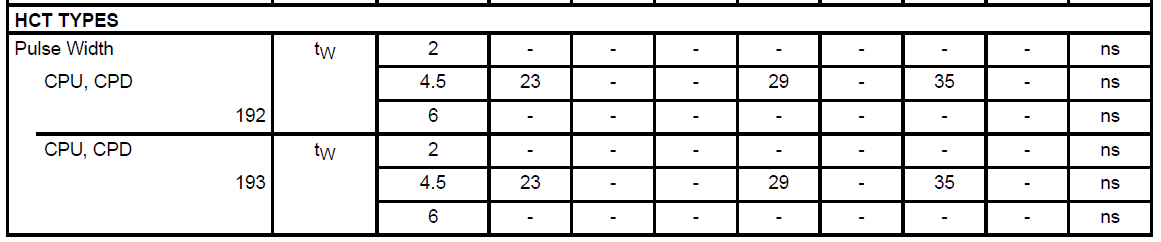

Lets look first at the propagation delay of the 74HCT00: the spec sheet says typical t=10ns, max t=25ns.

So lets measure the timing diffence between the clock and the output of the NAND gate. First line is the clock, second line is the NAND out signal.

Here the measure is 10ns (one sample of my analyzer). It's in line with the specs.

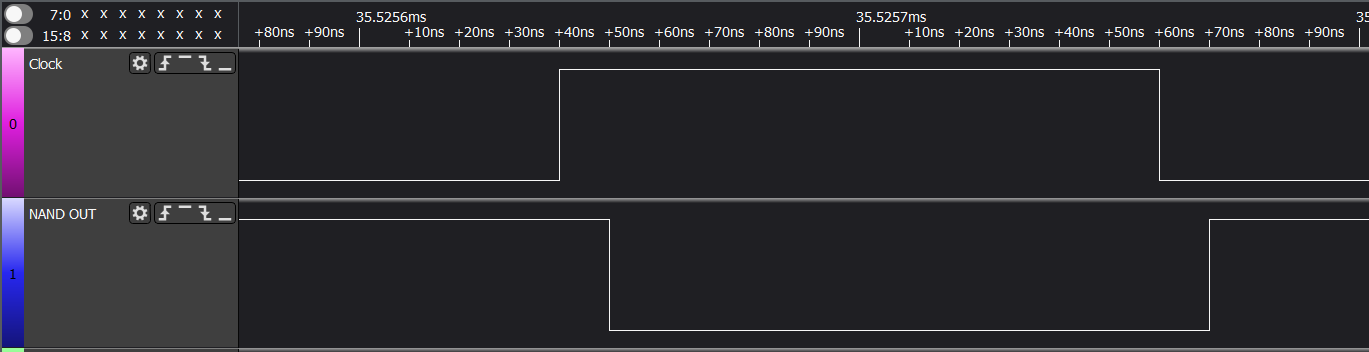

Step 2 - Delay to decrement the first 193

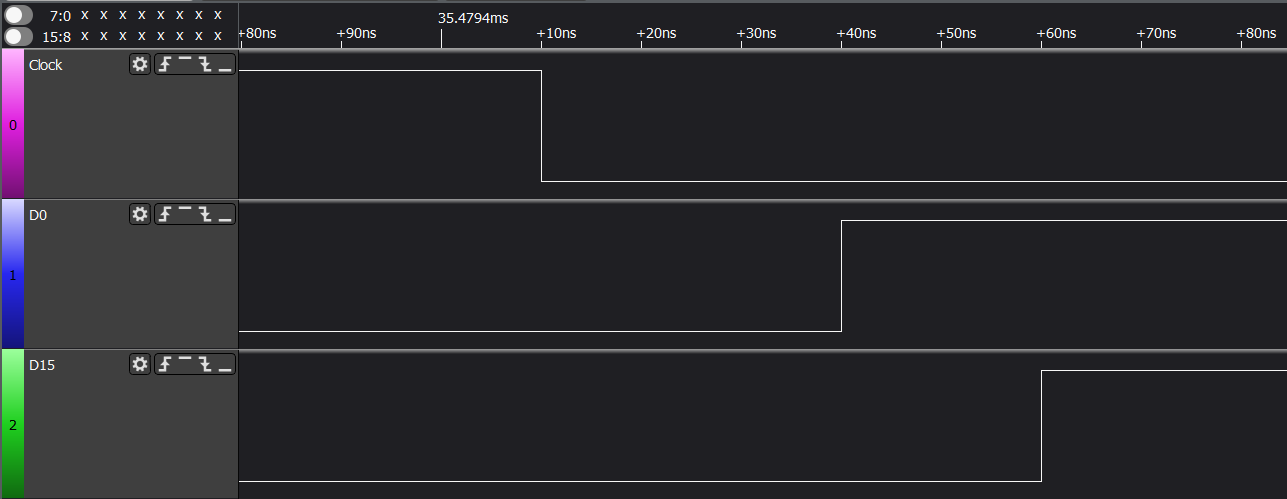

So now we measure the time it takes to decrement the value of the first counter. We select a specific moment, when both the first bit (D0) and the last bit (D3) of the counter switch (the counter decrements from 0b0000 to 0b1111)

The propagation delay is measured at 30ns from the clock signal, so lets say 20ns from the NAND out signal for the first bit and 40ns for the last one, this is consistent with the specifications of the 74HCT193:

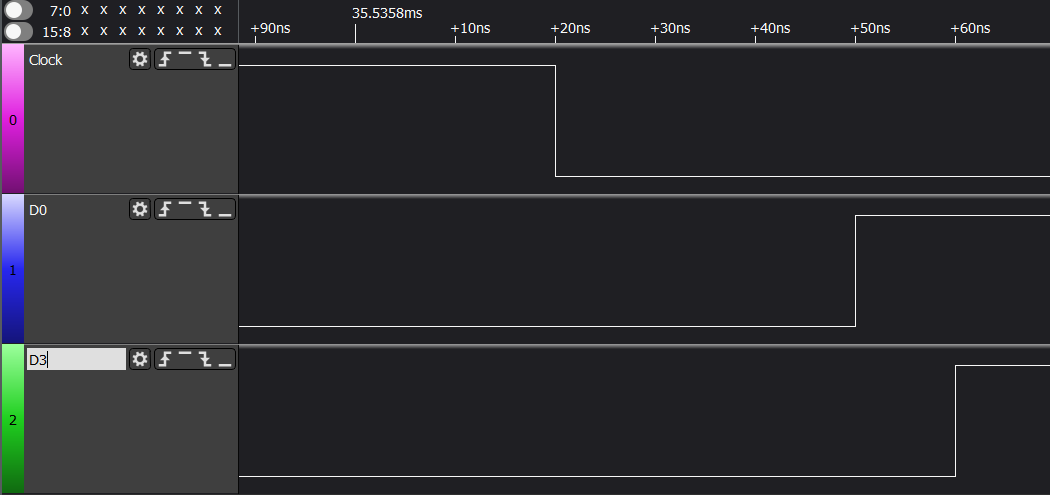

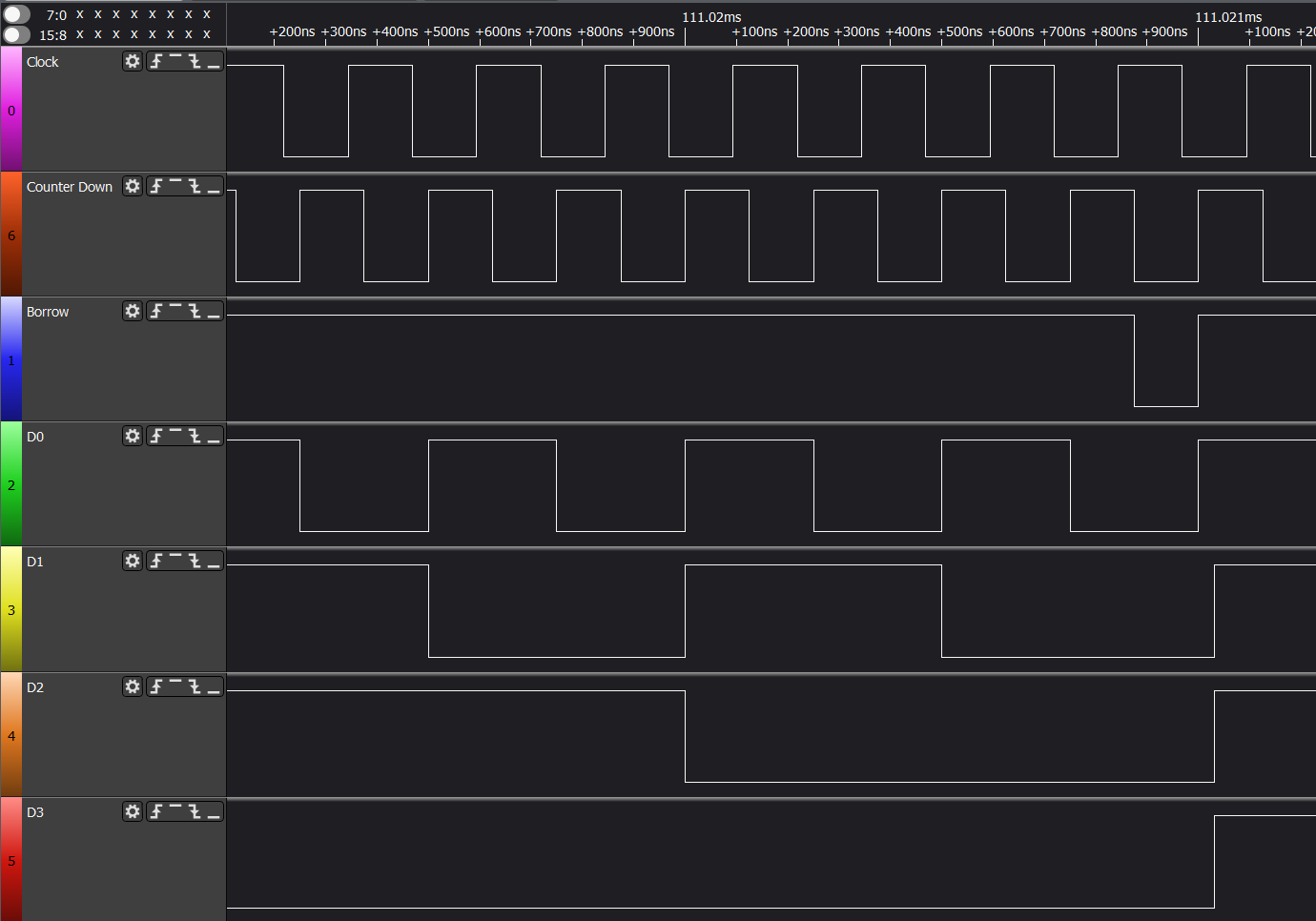

Step 3 - Delay to decrement all counters

For this final measure, we consider the worst case scenario where all counters need to decrement. We measure the difference between the clock, the first bit of the first counter (D0) and the last bit of the last counter (D15):

- Delay for the first bit: 30ns minus the NAND 10ns = 20ns

- Delay for the last bit : 60ns minus the NAND 10ns = 60ns

However, this is strange because how could decrement over 4 chained counters take only 40ns (60ns delay for the last D15 minus 20ns delay for the first D0) when one counter by itself takes 20ns?

The great trick of the 74HCT193

Well this great IC has a trick, it doesn't compute the result of the counting to consider sending a carry signal or a borrow signal to its neighbour. It already know before the computation that it will not be able to perform the compute by itself and sends the signal immediatly. This is called the look-ahead carry or borrow. Basically:

- If the chip value is 0b0000 and we want to decrement, it can send the borrow signal immediately

- If the chip value is 0b1111 and we want to increment, it can send the carry signal immediately

Here is a clear measurement of this features (remember we are decrementing so it is a borrow signal). Look at the area where all the values D0 to D3 are at 0, we can see that the borrow signal mimics the decrement signal. For all the other values of D0-D3, the borrow signal stays high.

Ced

Ced

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.