Before designing any of the cards for the computer, I needed to settle on the backplane connector and the signals on the main bus. RISC-V requires a pretty big internal bus to start with: each instruction can have two input and one output operand, and each of those operands can be one of 31 (well, 32, but zero is special) registers. This starts us out with 111 signals. Add to that a clock, memory control (read/write), and some space for other control signals - plus plenty of VCC and GND pins - and there aren't many inexpensive connectors that give us the requisite number of signals.

I eventually settled on a 3.3V 64-bit PCI connector for the backplane. This provides plenty of signals for our needs. I'm dedicating a lot of pins to power in this design - I tried to sort of guess from the design of PCI itself how to lay out signals on a connector like this. If anyone has suggestions for resources on backplane design I'd happily take them.

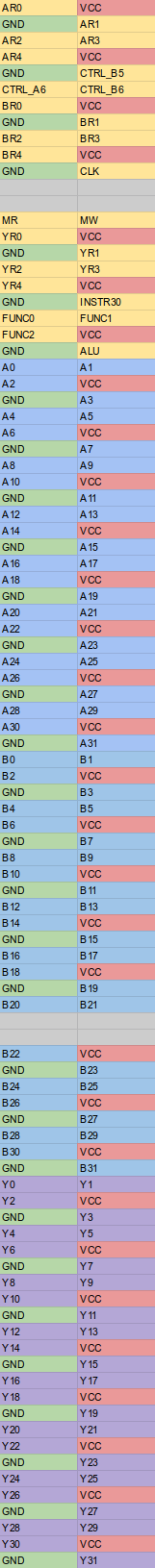

The groups of signals are as follows:

- AR{0-4}; BR{0-4}; YR{0-4}: The register selection signals. These control which of the 31 registers are selected for the two input (A, B) and the output (Y) operands of instructions. A zero indicates no register is selected, and something else is driving A or B, or receiving Y.

- A{0-31}; B{0-31}; Y{0-31}: The data for the two inputs (A, B) and the output (Y) of the current operation.

- CTRL_*: These are currently unassigned potential control signals

- CLK: The master clock. Positive edge triggered.

- FUNC{0-2}: The three "function" bits from a RISC-V instruction. Their interpretation depends on the other control signals. For an ALU instruction, they indicate which operation to perform. For a memory operation, they indicate the size of the load/store.

- INSTR30: This is essentially a fourth function bit, labeled separately due to how RISC-V encodes it into the instruction word.

- MR; MW; ALU: The operation type. "Memory Read", "Memory Write", or "ALU". This could probably be brought down to two signals if we were willing to handle a bit of extra decoding logic on each card, but there are extra signals right now.

Below is the bus, as currently specified. Gray boxes indicate the keying positions in the PCI connector.

Branan Riley

Branan Riley

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.