As a reminder:

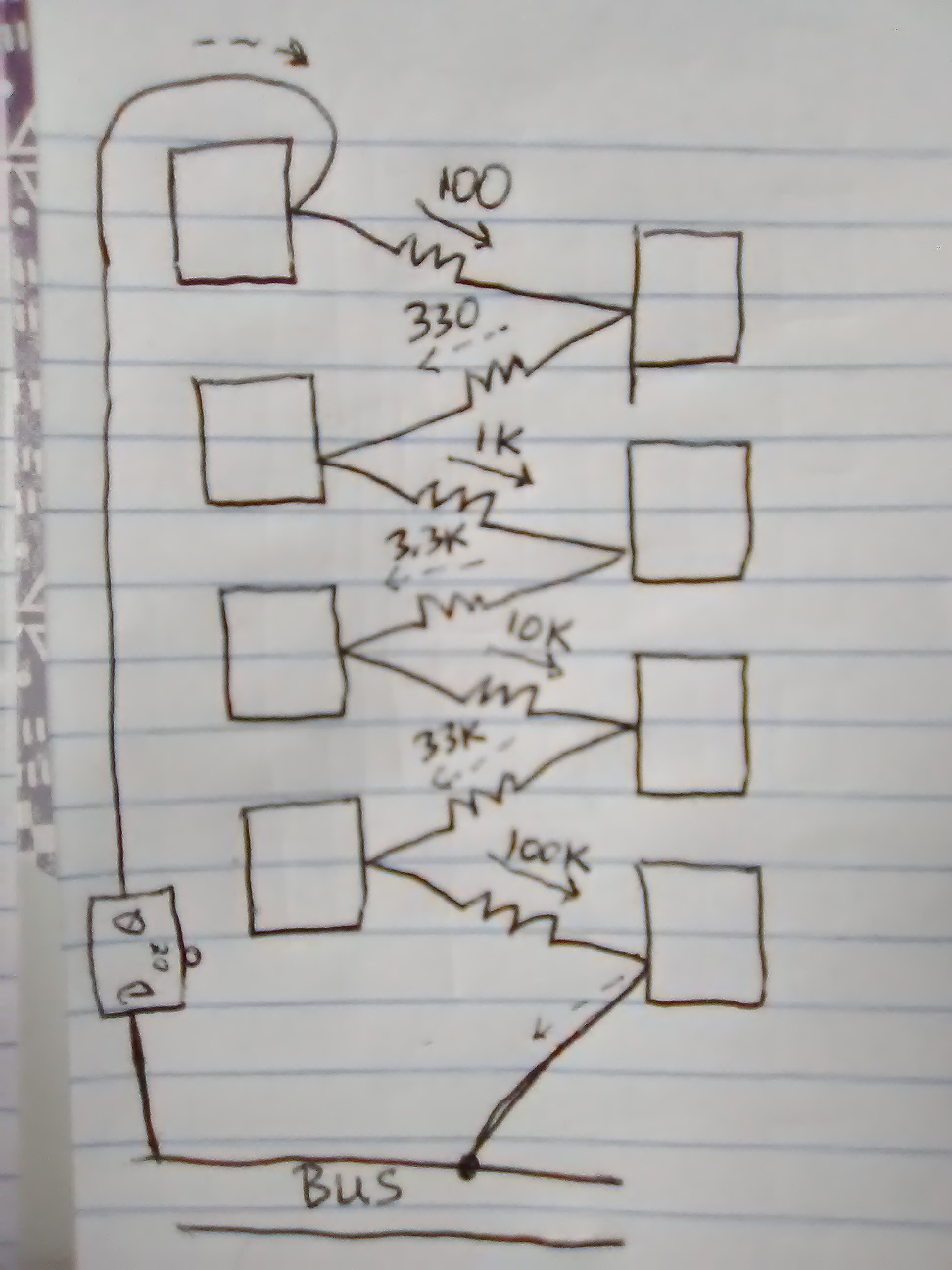

We have two independently-controllable banks of RAM, each of 4 chips [Left column and right]. These banks are wired together in such a way that all 8 chips can be accessed by a single r/w connection to the data bus through a sort of march ("Left right left") of the data.

Today's waking thought is much like the other day's "duh moment" [in a previous log]. WE HAVE TONS OF RAM. For some reason, last time I made that observation, I didn't get the full implication!

Last time I realized that to read-back the left column, I don't have to destroy the data at the same addresses in the right column, so therefore could read-back any address from the left to any address on the right. Like, for instance, a dedicated address for the shear purpose of a temporary shift-space. YEAH!

But, for some reason I hadn't made that same observation the other way. Thus, it was expected that read-back from the left column would inherently shift the data stored there from chip to chip, and eventually out of the column entirely.

That's fine for most intended cases; #sdramThingZero - 133MS/s 32-bit Logic Analyzer uses the left column for the realtime sampling of data, and in most cases will be connected to a computer with plenty of its own RAM to store the samples internally once transferred.

BUT: the original data, in the left column, *doesn't* have to be destroyed, nor even shifted, because, again, WE HAVE TONS OF RAM. So, another dedicated temporary location can be used in the left column, TOO! [DUH!]

And now, #sdramThingZero - 133MS/s 32-bit Logic Analyzer can use this method to connect 64 data bits to an 8 bit bus and is no longer limited to computers with lots of RAM; can be used with a PC/XT, a Kaypro, a Gameboy, or an AVR-based arduino, as I'd intended from the start. WEEE!

[And another thought on using this same method to *serialize* the 8-bit bus down to a single bit?!]

[And maybe the DQ latch could be replaced with a buffer with /OE, buffer output tied to the first 'chip' in the right column, since sdramThingZero has no reason to *write* to the sample-memory... hmmm... OTOH, there's little reason to *read* the right-column, either... main reason is just to make certain it wrote correctly... so there may be room for even further optimization]

Hey HaD!!!

Please do something about the editting of logs' sometimes deleting images! All I did was add that last bit in brackets, and hitting backspace[?] somehow deleted the image numerous paragraphs above?! This is nowhere near the first time.

Eric Hertz

Eric Hertz

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.