I was not satisfied with the performance of the previous version of PZ1_Pico, too many cycles were spent driving memory. So I went in the direction of CPLD to see how far that would take me.

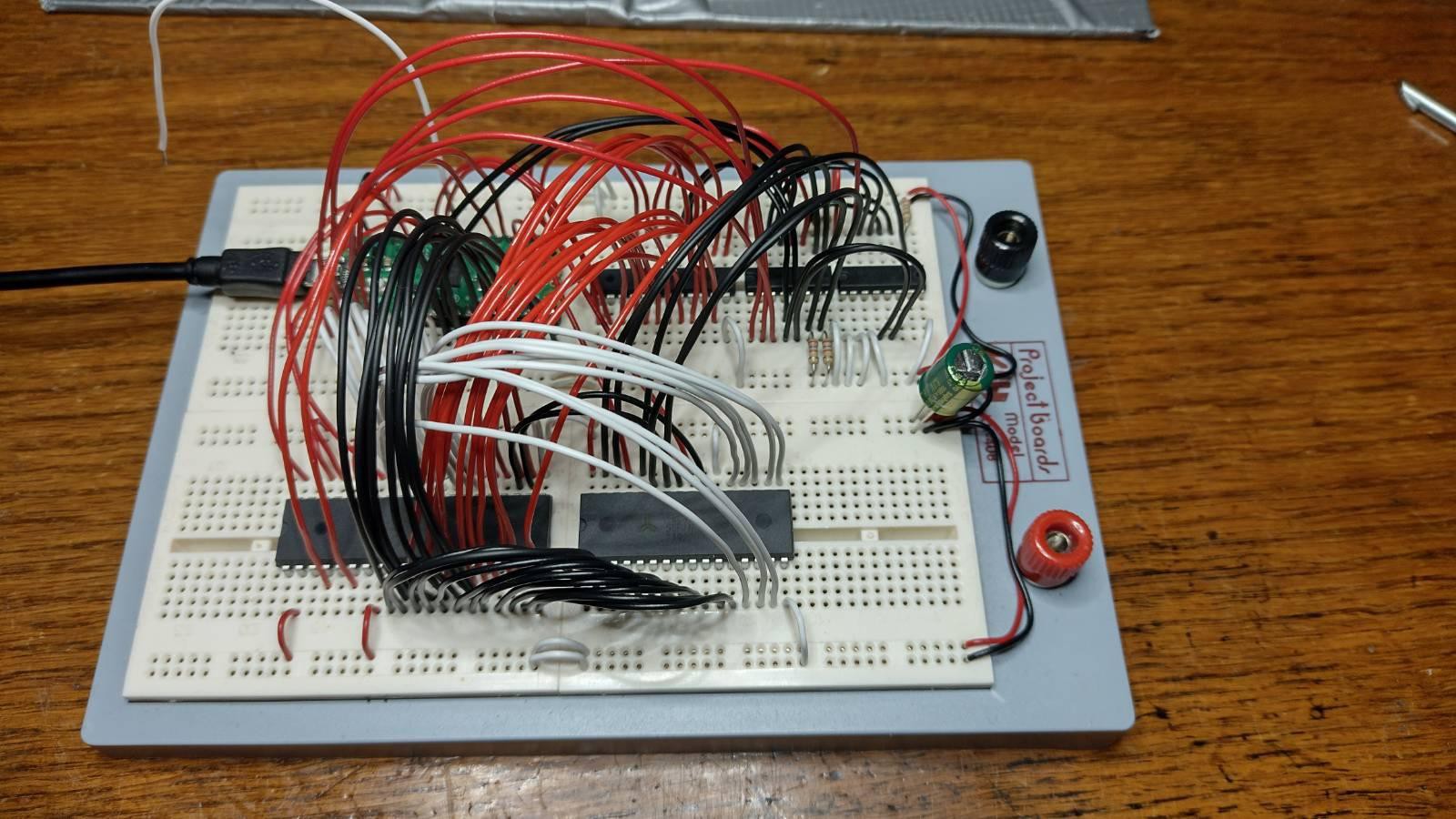

It turns out quite far. With an unbuffered addr/data interface and an overclocked Pico, I could run the 65C02 @8MHz on the rats nest pictured below! The CPLD (ATF22LV10) performs RAM timing/decoding and there are 2x 74HC670 to deal with banked memory. The Pico handles top page ROM duty as well as all I/O-devices implemented. It also drives the CLK of the 65C02.

I REALLY didn't expect this to work at these speeds! I thought the 74HC670:s and the bread board would be big hurdles to reach much more than 2MHz, but I was obviously wrong.

This is not the final result, I've already built a version that adds 2 buffers for the data/addr so it is possible to get the number of used Pico-pins down to only 16 for interfacing with the 65C02 and CPLD. That leaves 10 gpio for all the I/O I want to drive, just like on the PCB-version. That is an even messier rats nest that will not show up in this post :)

There is a major problem with this implementation: the global chip shortage has most CPLDs I've looked at in severe scarcity. I have a few chips that I can make my prototypes with, but I couldn't build any more if I wanted to.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.