The 68000 CPU IC had a pin called DTACK* (Device Transfer Acknowledge). When you grounded DTACK* the CPU ran at full speed. If you wanted to slow down the CPU for a slower external device you pulled the pin high until the device finished.

The FPGA Core for the 68000 CPU has a similar pin "clkena_in" which flips the sense of DTACK* and "stretches" the clock when it is low and enables the CPU clock when high. The pin was set to high in my design and there were no wait states. This didn't work for External SRAM so I lowered the clock speed to 16.7 MHz which allowed the CPU to access slower External SRAM correctly.

Adding Wait States to Speed up the CPU

I added a wait state counter for the clkena_in signal which is activated when the CPU tries to access External SRAM. This will come in handy if I want to get the external SDRAM working. Here's the code for the wait state counter plus part of the CPU instance..

-- Wait states for external SRAM

w_cpuclken <= '1' when n_externalRam1CS = '1' else

'1' when ((n_externalRam1CS = '0') and (w_wait_cnt >= "0100")) else

'0';

-- Wait states for external SRAM

process (i_CLOCK_50,n_externalRam1CS)

begin

if rising_edge(i_CLOCK_50) then

if n_externalRam1CS = '0' then

w_wait_cnt <= w_wait_cnt + 1;

else

w_wait_cnt <= "0000";

end if;

end if;

end process;

CPU68K : entity work.TG68KdotC_Kernel

port map (

clk => w_cpuClock,

nReset => w_resetLow,

clkena_in => w_cpuclken,

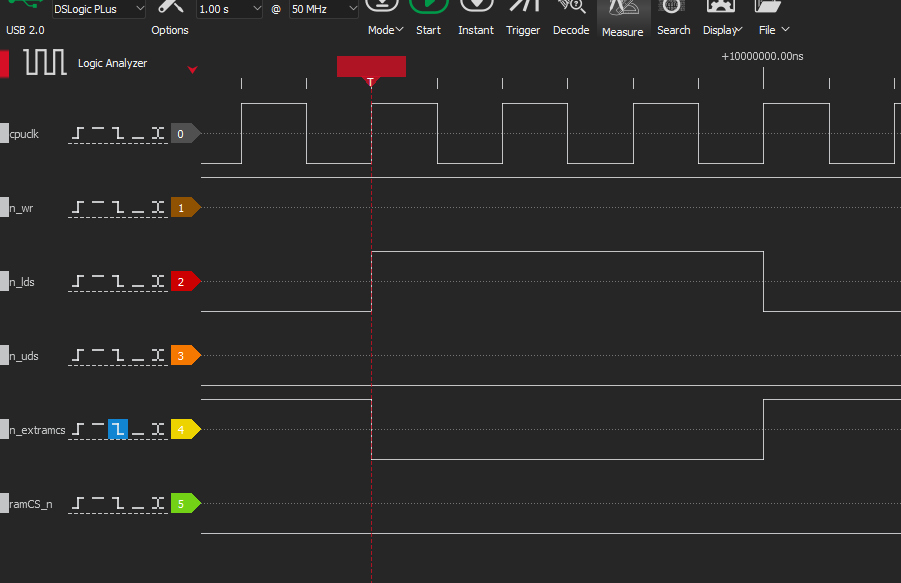

As a result I was able to move the CPU speed back to 25 MHz with no wait state for any other accesses.

The External SRAM chip select is now 120 nS (3 CPU clocks). It could easily be made shorter since my External SRAM is 45 nS parts. Would still need additional time for propagation delays and setup times so I will leave it as is for the moment..

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.