In order to see if the generated video signal is good or not, one simple trick is to pre-populate video RAM with image as if CPU had generated it.

I used two images:

TIM-011 signal generator on Anvyl - my lame MSPaint image:

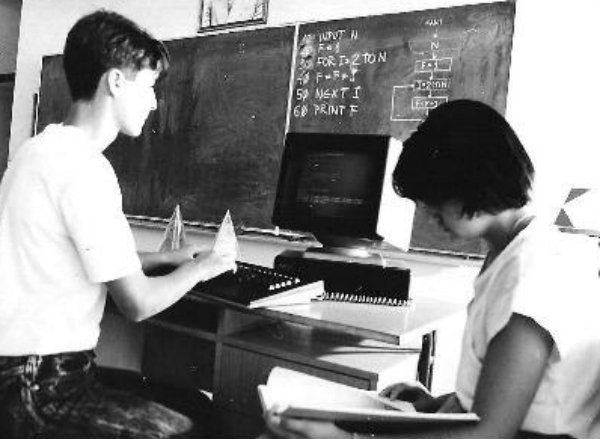

TIM-011 sampler on Mercury - model students busy learning Basic from original 1988 ad (I hope I am not breaking their copyright!)

Of course, both of these converted to 512*256*4 colors look a bit less impressive...

All FPGAs support initializing RAM/ROM which is part of the design. However, the file format varies. As I was using Xilinx ISE14.7, I needed .coe file to include into project.

Here are steps to generate the .coe:

1. Convert image to .bin file using Img2Tim utility which will:

- Ingest .png, .jpg, .bmp file and instantiate a memory image object from it

- Resize (squish) to 512*256

- Sample the colors using simple thresholds to get only 2 bits per pixel

- Use the knowledge of TIM-011 video memory organization to generate 32kB .bin file

(use Img2Tim.cmd)

2. Once we have the .bin file, use file conversion mode of my microcode compiler to generate .coe from .bin

(use mcc.cmd)

3. Finally, use ISE native tooling to generate the RAM component and point it to .coe file

There are other approaches too - for example, tooling could generate VHDL source code directly that initializes the memory and include that file into the project to be compiled, but such file would be very large and slow down compilation. mcc is able to generate VHDL from .bin file in case non-Xilinx approach is needed.

zpekic

zpekic

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.