Theory of Operation

Block Diagram

The driver of the show is the FPGA, it's a 10M08SAE144I7G from the Altera MAX10 Series. MAX10 devices are cool because they have a built-in configuration flash memory and some UFM (User Flash Memory) that can be written when the FPGA is programmed to store non-volatile data. This project uses the UFM to store code for the CPU.

The driver of the show is the FPGA, it's a 10M08SAE144I7G from the Altera MAX10 Series. MAX10 devices are cool because they have a built-in configuration flash memory and some UFM (User Flash Memory) that can be written when the FPGA is programmed to store non-volatile data. This project uses the UFM to store code for the CPU.

The clock is provided by a 10Mhz TCXO oscillator, a potentiometer connected to the adj. pin is used to adjust the frequency.

First, the signal is generated digitally inside the FPGA, then it goes into a 12bit R2R DAC that converts it to an analog voltage. The signal then passes through an inverting op-amp where a DC offset is added. After that, there's a VGA to control the output level. The signal is then filtered by an active op-amp filter before entering the final amplifier.

FPGA Internal Structure

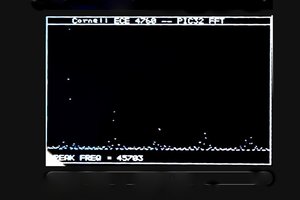

This block diagram describes the interaction between modules inside the FPGA. All components are memory-mapped on the same bus and are all controlled by the CPU. The CPU is a NIOS II Soft Core provided by Altera, it executes code directly from FLASH. It handles all the user interface stuff like responding to button presses, updating the screen, and talking to the SD card.

This block diagram describes the interaction between modules inside the FPGA. All components are memory-mapped on the same bus and are all controlled by the CPU. The CPU is a NIOS II Soft Core provided by Altera, it executes code directly from FLASH. It handles all the user interface stuff like responding to button presses, updating the screen, and talking to the SD card.

The second main module is the DDS Core, there are two of them, one for each channel. The DDS Core is responsible for the generation of the output waveform. Each DDS Core interfaces whit the CPU through three look-up RAMs and a control bus. Waveform parameters like frequency, modulation depth, etc. are set via the control bus. Waveform shape is controlled by the look-up RAM. The CPU can update the look-up RAM content at any time. When a wave file is played, the CPU loads samples from the SD Card into the proper look-up RAM. The output frequency is set equal to the wave file sample frequency therefore, the DDS Core reads one sample at a time from memory and reconstructs the signal. When half of the samples are consumed an interrupt is triggered and the CPU replaces that half with new data.

DDS Core

This module is a wrapper around three Wave-Generator modules. One of them is used to generate the main waveform, the others are for frequency and amplitude modulation. The CARRIER_PHASE_STEP input is the frequency of the unmodulated waveform, a signal is added to it to achieve frequency modulation. Amplitude modulation is applied to the signal at the end.

This module is a wrapper around three Wave-Generator modules. One of them is used to generate the main waveform, the others are for frequency and amplitude modulation. The CARRIER_PHASE_STEP input is the frequency of the unmodulated waveform, a signal is added to it to achieve frequency modulation. Amplitude modulation is applied to the signal at the end.

Wave Generator

This module takes samples from a look-up RAM and outputs a waveform. Frequency is selected with the PHASE_STEP input. The PHASE_OFFSET input adds a phase offset to the waveform. The memory controller looks at the current phase to generate the appropriate address to index the look-up RAM.

This module takes samples from a look-up RAM and outputs a waveform. Frequency is selected with the PHASE_STEP input. The PHASE_OFFSET input adds a phase offset to the waveform. The memory controller looks at the current phase to generate the appropriate address to index the look-up RAM.

Future Improvements

- Add a cache memory between CPU and FLASH. Without that code runs slow and the user interface is not super responsive.

- Upgrade to a bigger FPGA with more UFM. UFM is too small to fit any more code, thus the SD card functions can't be fully implemented.

- Use a proper DAC IC. The R2R DACs are inadequate, even with 0.1% resistors the nonlinearity is too much.

References

Manuel Tosone

Manuel Tosone

Bruce Land

Bruce Land

Erik Piehl

Erik Piehl

Wenting Zhang

Wenting Zhang

rusher

rusher