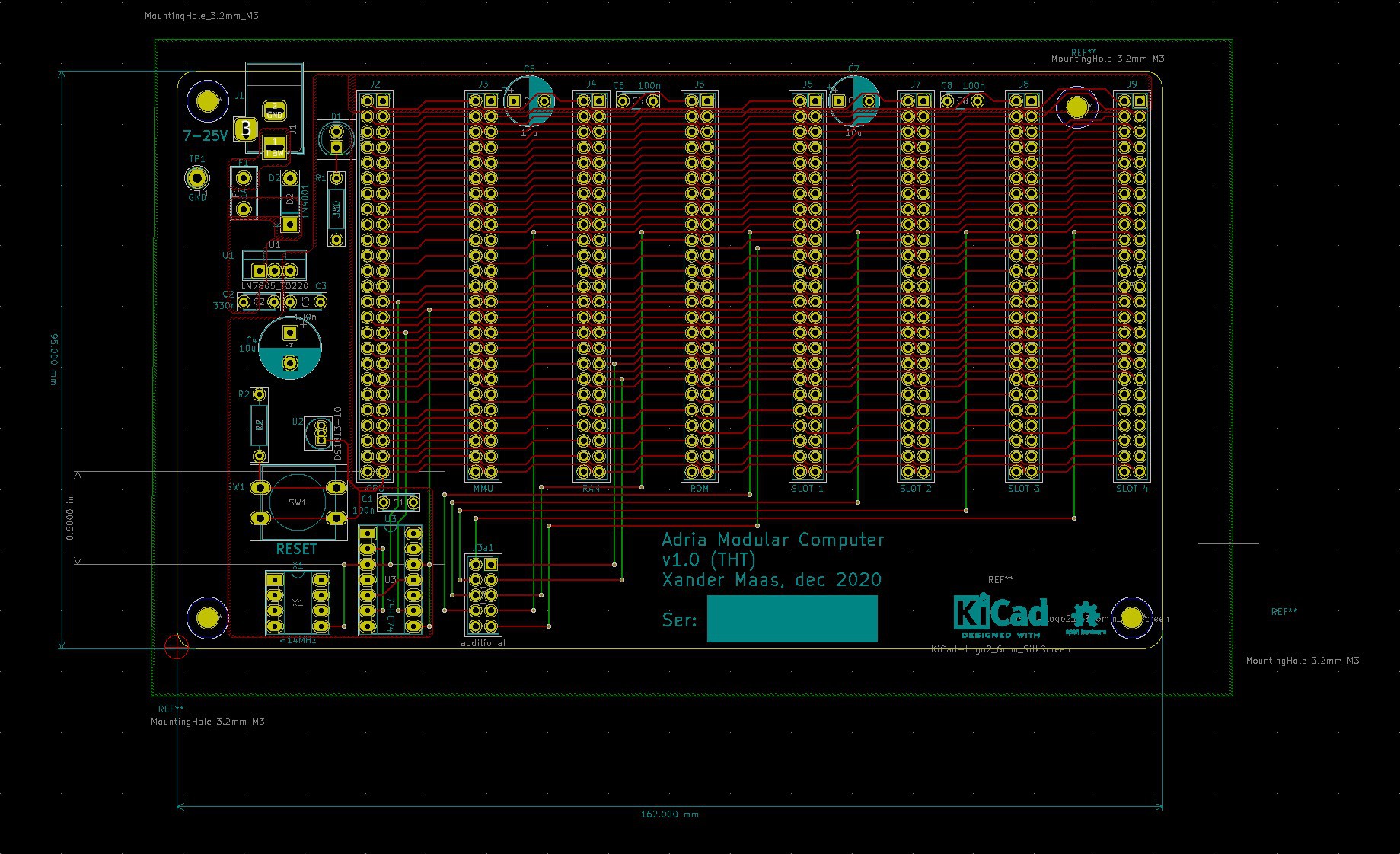

The project has been started in december 2020. A first run of boards has already been done, as has a second run.

In the meantime, I have updated the backplane to a 4-layer PCB, with ground and power (+5V) in the inner layers and signals routed at the top and bottom layers. These haven't arrived yet, but should in a few days. This new (4-layer) revision should make it possible for me to run the computer at higher clock speeds.

Also the first run of the backplane had some "small" issues:

- U3 missed the feedback from pin 8 to pin 12 (/PHI2) for the clock divider

- Missed all /IRQ and /NMI traces to and from the CPU slot and all peripheral slots

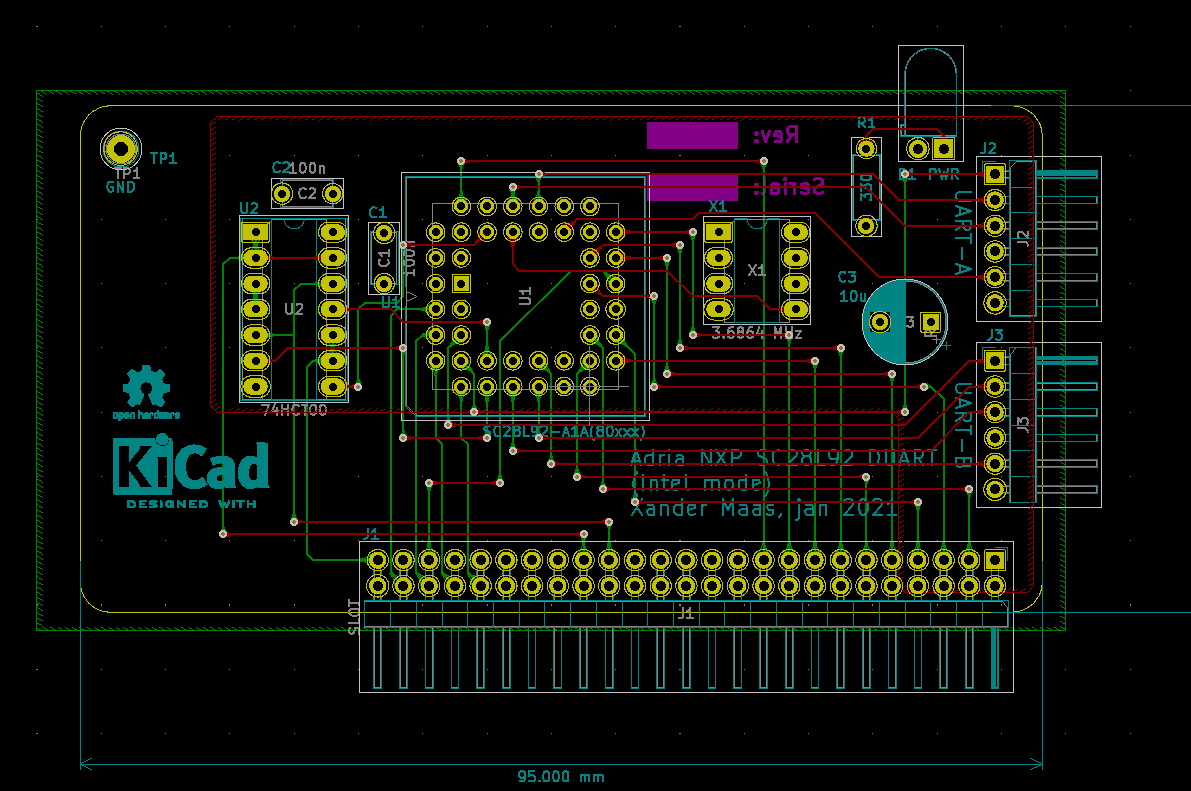

Also I have had a few 6551 (I used a SY6551) UART and NXP SC28L92 UART boards manufactured. With the help of some great people at forum.6502.org, I now have a working driver in ROM for the SC28L92, so the (speed) limited 6551 board isn't in use right now.

Xander Maas

Xander Maas

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.