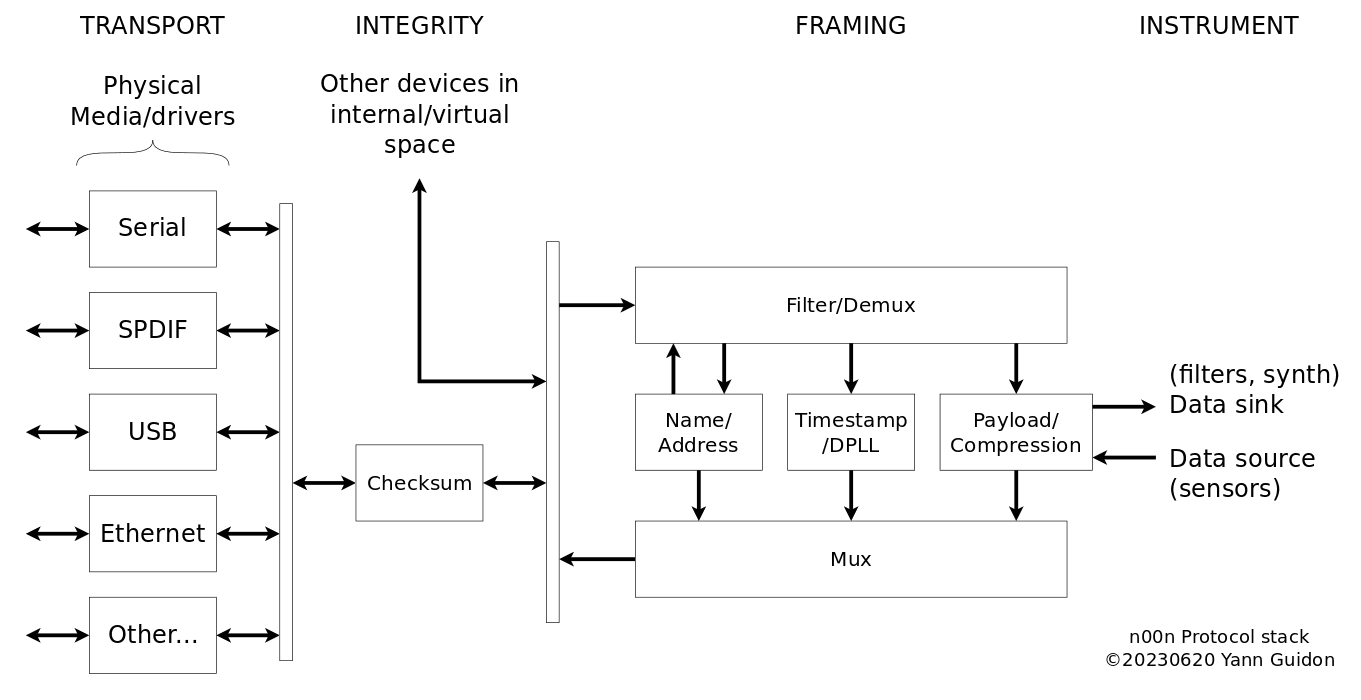

Software blocks should be reused as much as possible, if, how and where needed. The same code is used for the generators (timing/tick/global clock), the transceivers (instruments, recorders) or the receivers (synthesisers). This should even be independent from the actual interface or topology of the links between the devices.

- The only variable module is the "Transport" which interfaces with either SPDIF, USB, serial, Ethernet... This Transport Module manages the topology, the eventual buffers and multiplexing, connexion/disconnect events, and crude filtering. There can even be a "null" transport inside the computer, VST-like.

- Incoming and outgoing packets then go through the checksum module : the checker/generator(s) can be separate if needed but it's basically the same thing.

- From there on, each data packet is considered destined to/coming from the device, inside the memory space of the processor. The null transport can connect directly here, bypassing the checksum module. The packet is assembled and/or dispatched by a mux/demux. There are at least 3 sub-modules that do the actual processing (we're getting there at last):

- The name/address module manages the filtering, the serial number, the dynamic address, the user label... so it is closely linked to the transport layer.

- The timestamp module receives clock events, keeps an internal timebase at 65536 Hz (or more) so it can generate fractional timestamps for internal events, in sync with the external timebase. It contains a sort of DCO or "digital PLL".

- The instrument module does the real data stuff. It can receive external configuration messages, or data streams, but mostly emits data.

- The Instrument module streams can go through an optional compression module to save bandwidth.

Note: some internal messages could be created for the init, connect and disconnect events...

With the modular architecture, each module can be included depending on the type of device : timestamp generator, sensor, recorder, filter, synthesiser...

Furthermore, the packet format has a separate checksum for the payload and the header so the addressing and the timestamp modules can be addressed without waiting for the payload checksum to be completely received.

.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.