AX58100 Board design

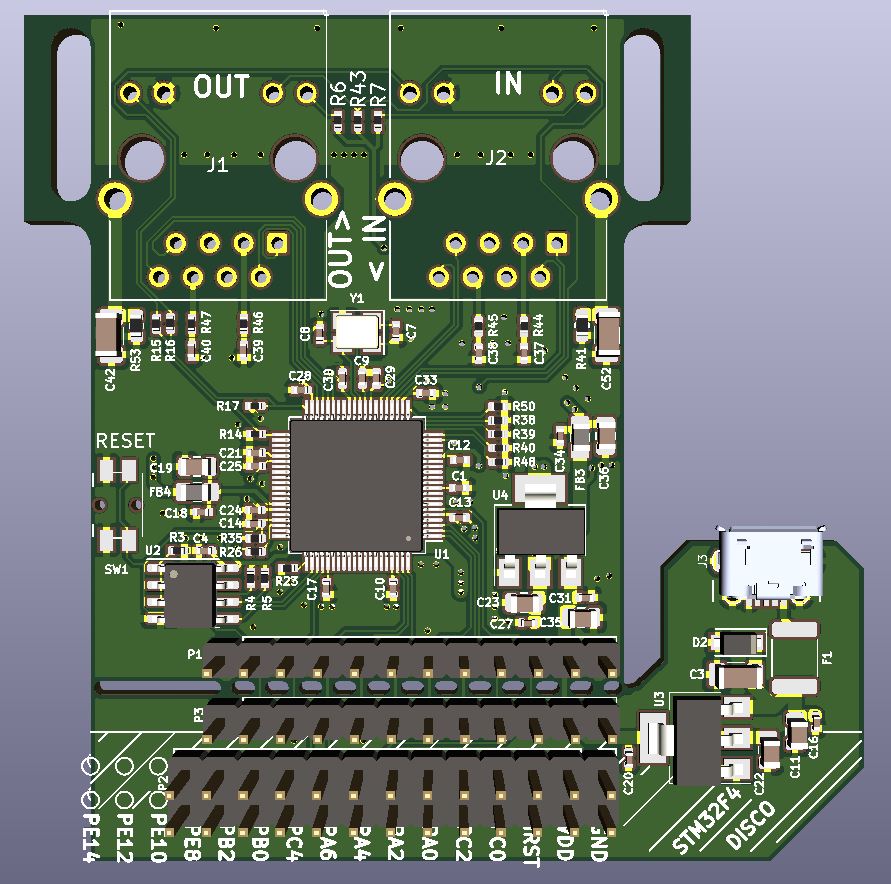

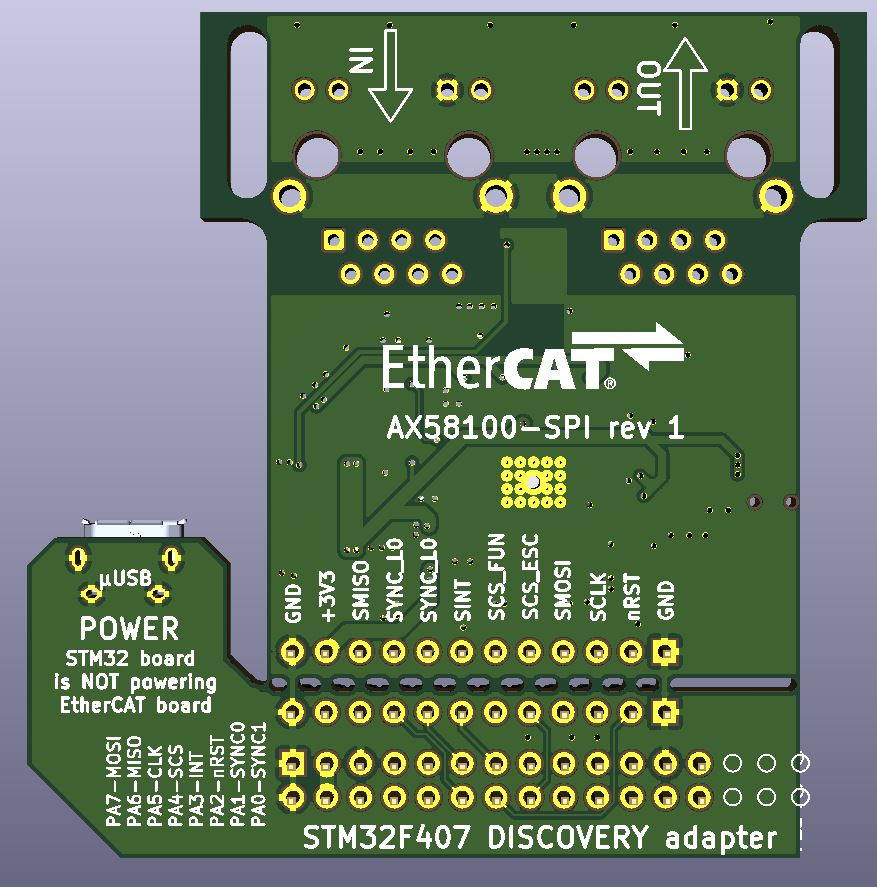

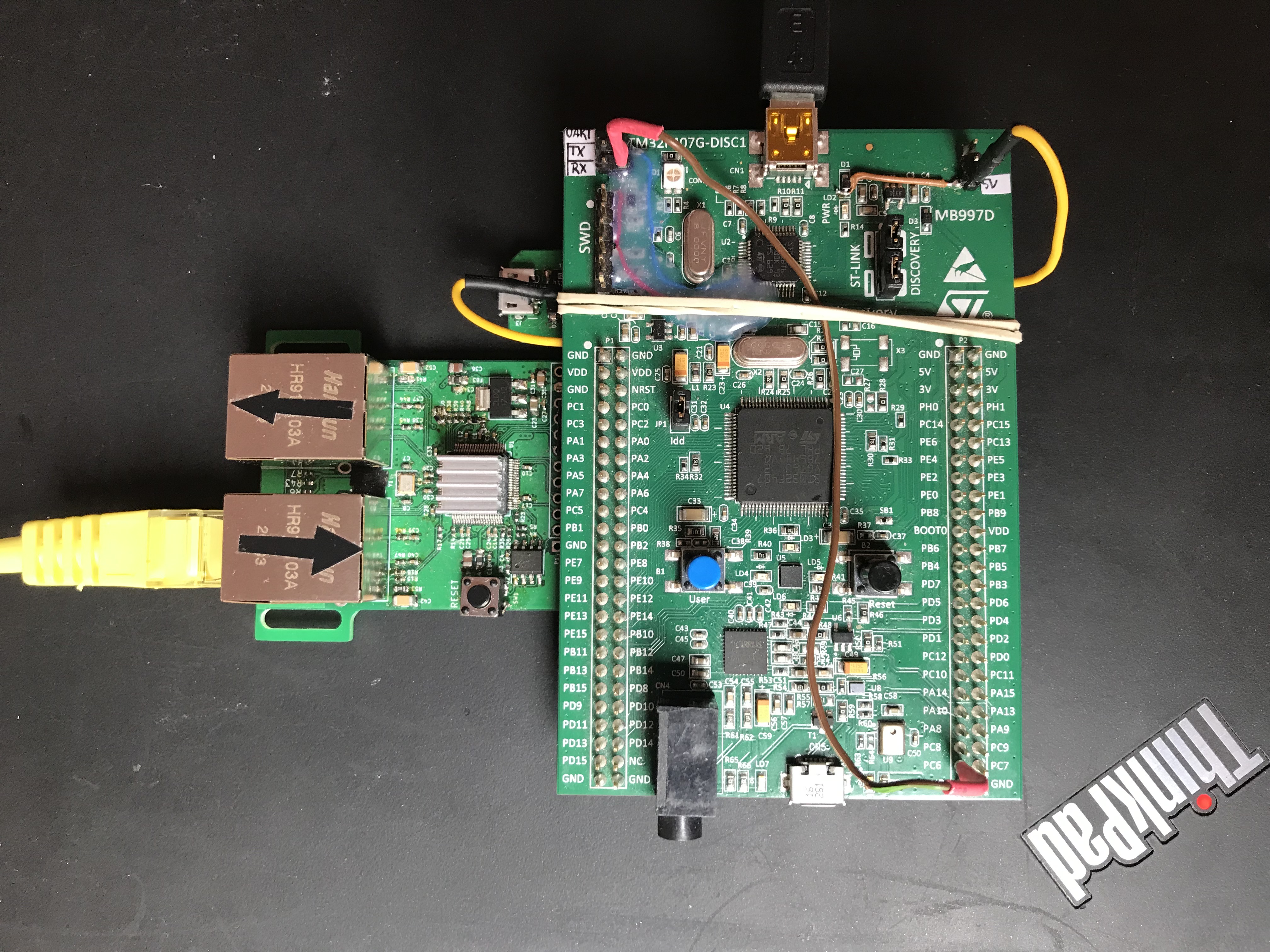

LAN9252 indirect register addressing is complex … frankly it feels cumbersome. Building DMA for that is certainly possible (with few state machines and plenty interrupts) but super messy and not that efficient either. The original ESC from Beckhoff, ET1100, was much more straigtforward to work with. To see the difference, just compare SOES HAL files for ET1100 vs LAN9252. Look at line count of respective files should be enough. Unfortunately ET100 costs 2-3 times as much and requires more external elements. Luckily, we can eat the cake and have it too thanks to ASIX, Chinese company I have never heard of before. They got license from Beckhoff and made improved derivative, AX58100. ASIX chips are not really offered via typical western suppliers, but few Aliexpress sellers have it. I risked few dozen of $, and while waiting for shipping I also designed PCB based on LAN9252 second revision. This time STM32F4 Discovery adapter with 3.3V regulator (and separate USB for power) is part of PCB that can be snapped off like ST Link from Nucleo boards.

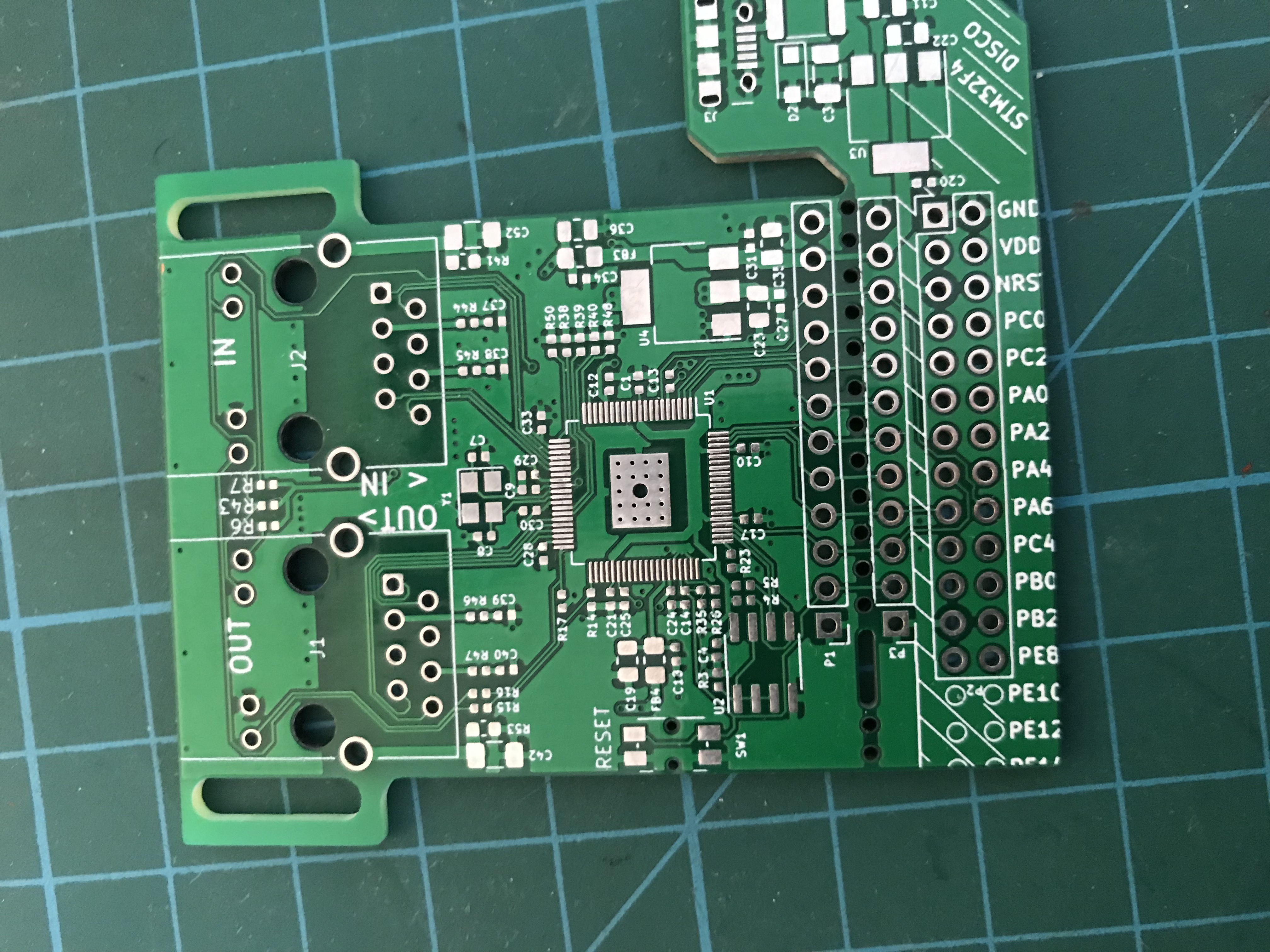

AX58100 board assembly

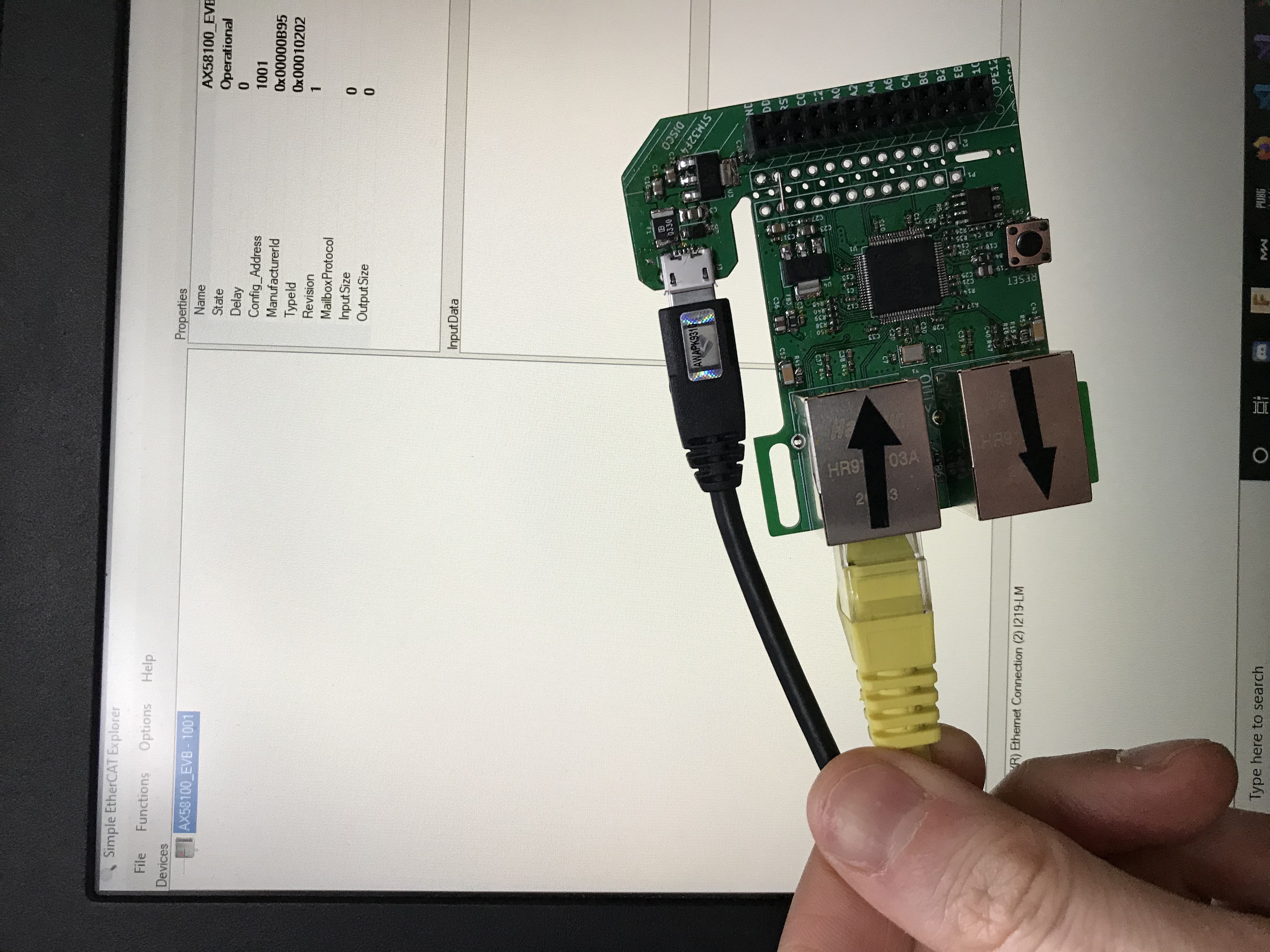

Repeating approach that worked with LAN9252, DIG IO ESI was flashed at first, and it was working right off the bat. Board is doing good so far.

AX581000 with SOES

This ESC is based on ET1100, and one of HAL setups in SOES source target this chip. As was with LAN9252, lets implement SPI read/write and go to town.

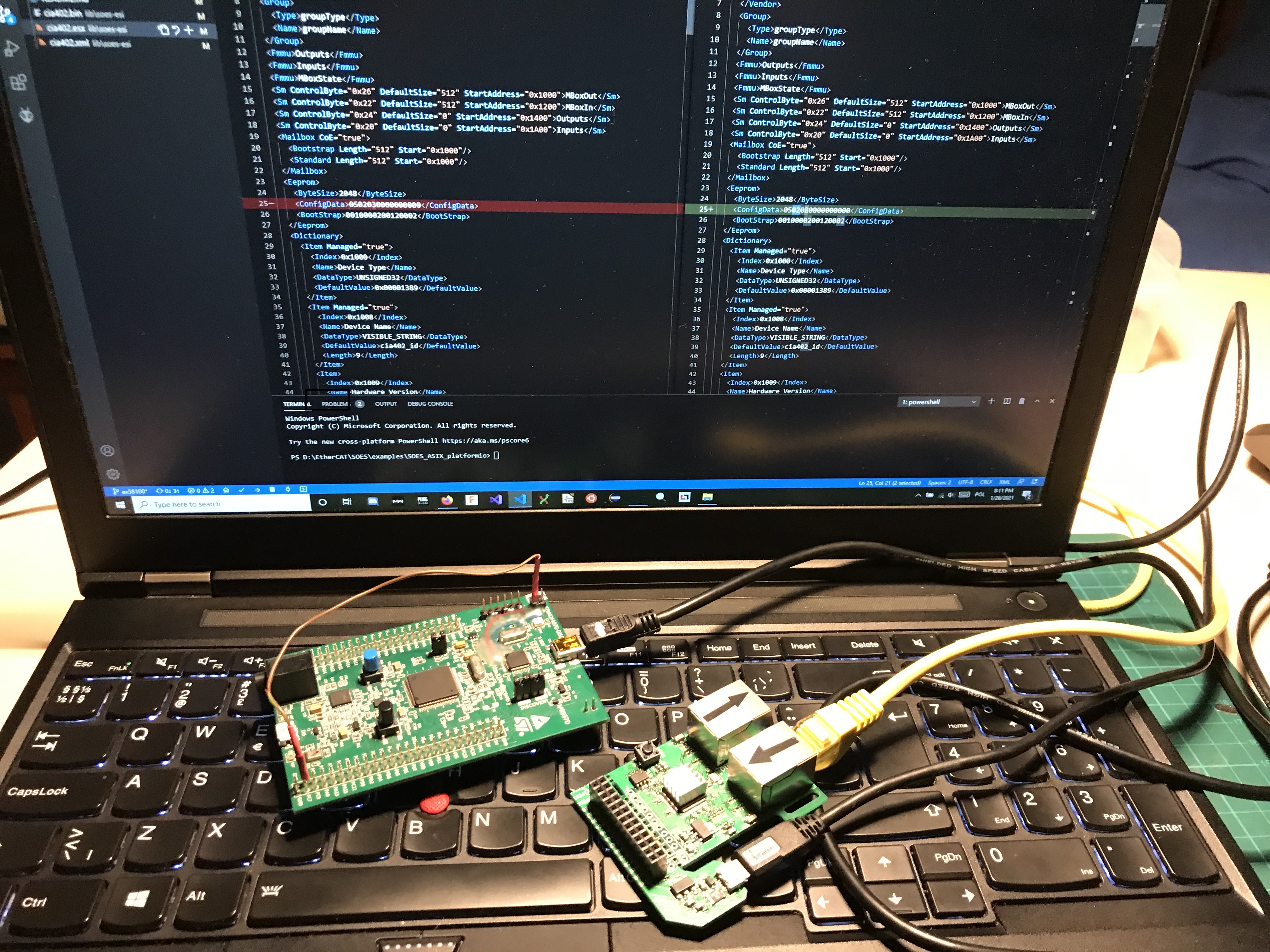

It is not working. Why? Let us check datasheet and manual for migration from ET1100. To enable SPI PDI, 4K7 pullup resistor to 3v3 is needed on SCS_FUNC. Is it enough? Hardware wise yes, overall no. Some configuration registers are different on AX58100. More head banging against docs ensures. AX58100 datasheet is rather short, what is missing there can be found in ET1100 datasheet. Luckily ASIX has code samples for STM32 Nucleo available on their webpage, and those include ESI files with correct configuration bytes. For SPI setup turns out HIES register (Host Interface Extend Setting and Drive Strength) which is mapped to configuration byte 0x0A, should be set to 0x1a (INT edge pulse length, 8 mA Control + IO 9:0 Drive Select). It is in area covered by checksum, so we need to calculate new one too.

After all that time and head scratching, new board is reaching OP with SOES application. Radiator was added to mitigate overheating while working on getting right PDI configuration in ESI file. Now that it is correct, feels like it is not probably wont needed will test on next boards.

Example: CiA 402 application on AX58100 with STM32F4

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.