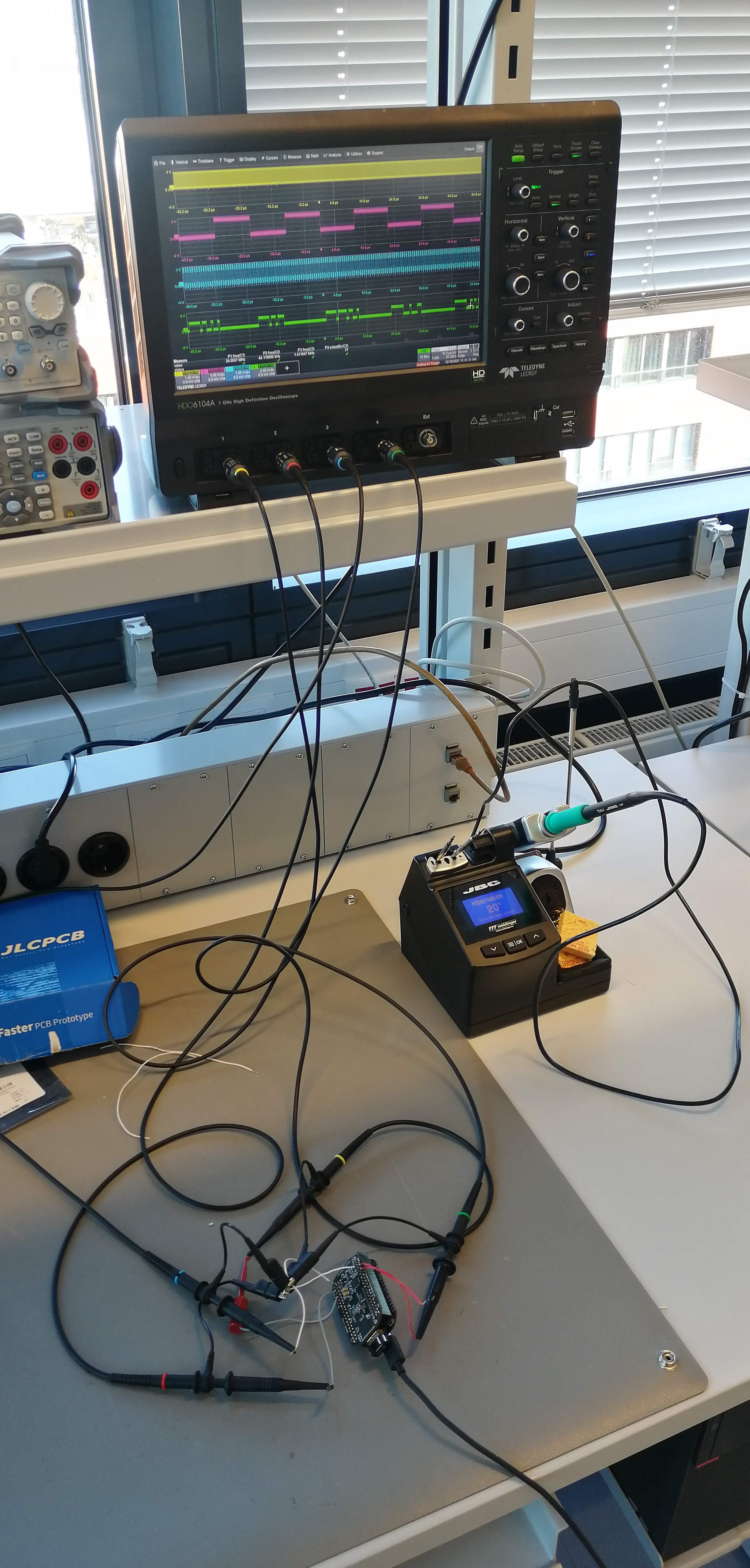

Hooking up my sound card to the scope revealed the following:

- Master clock at 24 MHz

- Word clock (a sample rate) at 44.1 kHz

- Bit Clock at 1.41 MHz

Knowing that desired audio file has the sample rate of 44.1 kHz, 16 bit resolution, and two channels, the bit clock of 44.1 x 16 x 2 = 1.411 MHz works out fine. Data is emitted only during the low-phase of the WCLK, which is unexpected, since the datasheet specifies that, in I2S mode, the data should be emitted in both phases (for the left channel during the low phase, and for the right channel during the high phase).

Pero

Pero

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.