The Changes to the Instruction set:

The MC14500 is primarily a 1-bit ICU. and thus, its not generally meant to do arithmetic (though it can through manual bit manipulation, it's not very fast.) Just as the UE14500 Project, our CPU will add a Add functions to add and subtract at a cost to some of the less useful functions. Unlike the UE14500, we will take things a few steps further and add a external command register. This will allow for moving memory and register values around 8 bits at a time, this will be done by adding a OP, code to facilitate switching between the 1-bit state machine and the external command register (which will also be a finite state machine.)

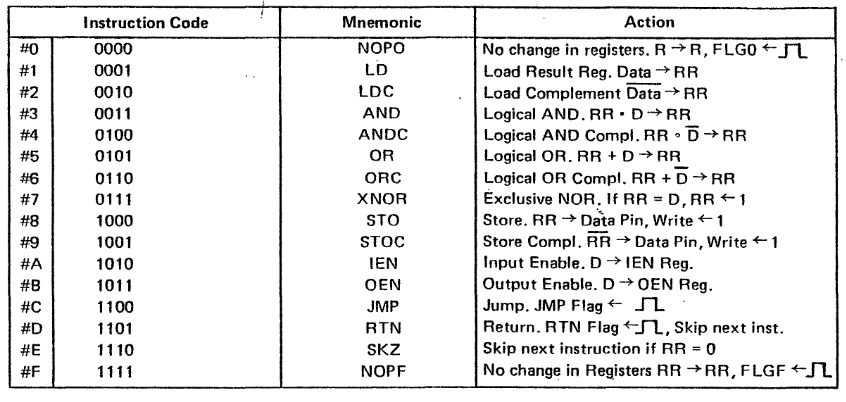

The MC14500 instruction set is as follows:

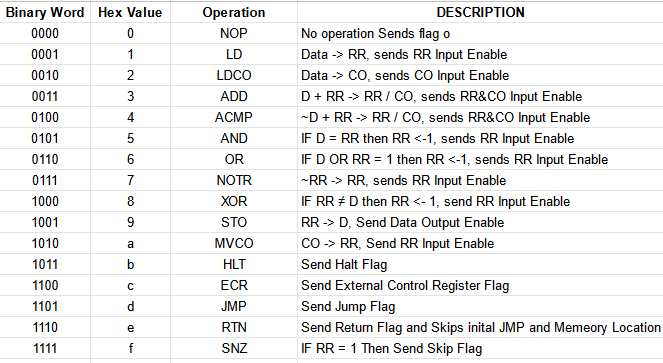

Our modified instruction set:

I've uploaded a preliminary diagram that shows how the logic would be laid out if we were building an actual CPU from gates. Since this a sate machine we really only care about the truth table, and you can think of this logic diagram only as a guide to how the logic works. The operation is simple, there is a 4 bit control word that sets how the output bits should output based on the 3 potential bit input lines coming from the 1-bit data bus the Results register, and the Co Register. The latched registers and flags all update on the falling edge of the clock cycle. the flags (with acceptation to the CO Input enable signal are generated via a 8 bit multiplexer control word (meaning only 1 flag on the output control register can be enabled at one time.) The CO enable signal is output separate because it is the only operation that updates both registers at the same time and a multiplexer can only output 1 output based on the 3 bit control word.

Subtraction:

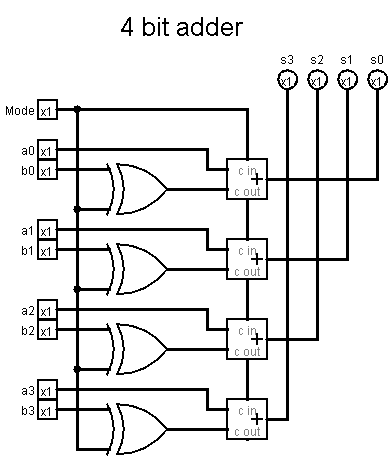

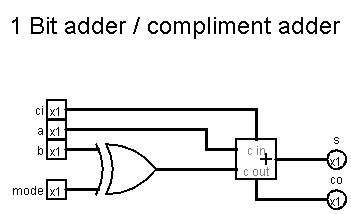

This CPU calculates data 1-bit at a time, though it actually looks at up to 3 bits to make a calculation, 1 bit from each register or the data bus, and a third carry bit stored from the previous operation. The first challenge of this is there is no real way to do a full subtract operation (at least not 2's compliment, though a 1-bit subtractor is possible, it's not used here). A full SBA (Subtraction by Addition) operation requires a XOR operation on the carry in bit, but only on the first operation. In a multi-bit adding scenario this allows for adding a 1 at the same time as adding the compliment of the second operand (to subtract and get a 2's compliment value:

As you can see the adder will add 1, but invert the inputs on the B input this works simply enough for a multi-bit operation as 4 bits are calculated at once. However this is slightly inconvenient when we try to do 1 bit operations. Thisi is simply because we can no longer use the CI line as a mode selection for every bit. The reason is simple; if we did that the adder would add 1 to each digit (this would not yield 2's compliment). Instead our CPU will provide 2 operations for arithmetic; add and add compliment.

This approach is slightly more cumbersome as the CI register has to be preset with a carry in bit (but only once). then each operation would add the compliment of the B register (when subtracting). Additionally this adds more functionality to the MU (math unit) as now the add compliment operation can be used to add the inverse of the B register to zero (allowing us to put it's compliment in the results register).

Dave Collins

Dave Collins

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.