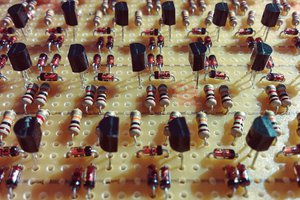

Browsing the web, I found a fascinating niche activity. People have built homebrew CPUs/computers using just basic logic chips. And they actually worked, they did real computation. These ranged from trivial 4bit machines, that barely did anything, up to impressive 8 bit machines that run a customized version of Mimix. One crazy guy in England has used several thousand transistors to create a machine that takes up half a room. They look cool, sound great fun to build and I want in on the action.

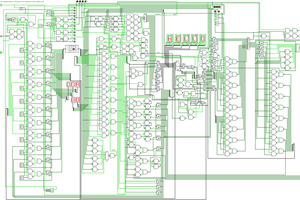

But what to do? Well there seems no point in just copying what others have done. The fun is in designing your own unique project and the journey taking it from idea to working machine. Well it seems worthwhile to tread new ground, do something not done before. As far as I can tell, there is no homebrew 32bit machine (I don't count an FPGA implementation). And certainly, none seem to implement a fully specified existing instruction set architecture (ISA). This is something that must change.

A bit of research later and I have found the perfect ISA. There is relatively new open source 32bit RISC architecture called RISC-V that has been designed by researchers at UC Berkeley. Being a RISC design, it is relatively small in the number and complexity of the instructions that need implementing. This is important as any 32bit design is already going to be a big project, so lets not make it impossible by going for something like the CISC of the 80386!

Phil Wright

Phil Wright

spudfishScott

spudfishScott

matseng

matseng

Yann Guidon / YGDES

Yann Guidon / YGDES

SHAOS

SHAOS

Hey there,

I want to do this as my undergrad's final year project.Can you help me out?