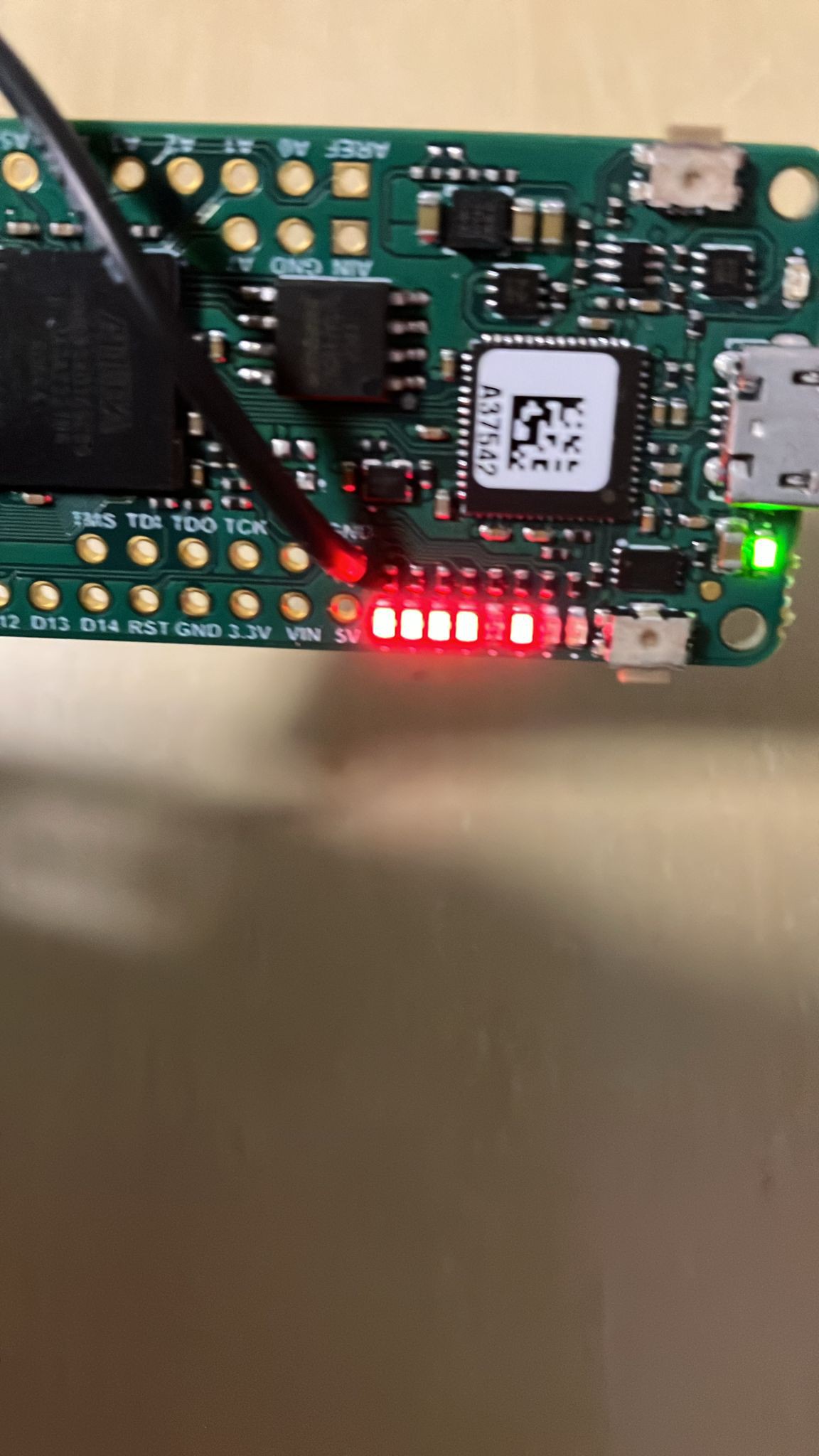

The following picture shows the result of calculating the integer square root of 60,000: 244 (1111 0100 in binary), computed by a relay CPU core implemented in an FPGA. The program running on the FPGA is the same as the one used on the relay CPU.

The FPGA will now be connected to the I/O register of the relay system and used as a mathematical coprocessor.

Peter

Peter

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Hi, you can download the VHDL Code in the download-area of my project page: RelCPUSQRT.zip. Best regards

Are you sure? yes | no

Bravo on this impressive projet.

It’s a great idea to use an FPGA as the digital counterpart of the relay computer.

Do you plan to use it as an emulator for the relay CPU, or as a true coprocessor attached to the system’s I/O?

If possible, I’d be interested in the HLV code, could you share it?*

Are you sure? yes | no