Luckily, the first prototype worked without real problems. The only obvious one being the strange footprint for the VGA connector.

But for my next pcb run, I want to do several changes:

- fix mistakes (VGA connector)

- add Mouse connector

- add HW for sending info to keyboard (and mouse)

- add memory bank select

- change video pixel/color generation

- change WiFi module type

- simple 4-wire connect to Raspberry Pi (file transfer)

BANKSWITCHING

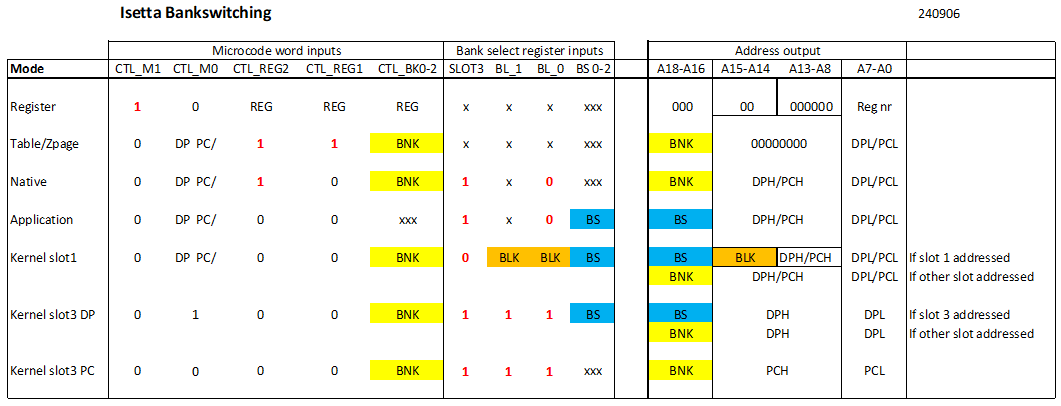

The memory bank selection is, I think, the most complicated of this new features. The new system will have the following modes: Register, Table/ZPage, Native, Application, Kernel slot1, and Kernel slot3. You can see that in the following table:

In the current hardware, only the Register mode, Table/ZPage and Native mode are present. The register mode allows access to 64 fixed locations in memory (a kind of zero-page addressing). There is another group of 64 locations that can be switched (for Z80 registerbank switching). Table/ZPage mode is used with an identity (1:1) table to access DPL and PCL, to access the Shift-right table, and for the 6502 to address ZPage values. The Native mode allows addressing the full 512 Kbyte of memory, but it's problem is, that the used 64K bank (yellow fields) is hard programmed in the microcode.

This will now be more flexible. In the new Application mode, one of the 8 selectable 64K banks can be programmed in a bank select register (blue fields). The selected bank will be valid for data as well as program code. Note that the microcode can force that Native mode or Register mode is used, by using the control bits CTL_M1 or CTL_REG2.

An operating system must be able to access all memory, to be able to load programs and move data around. I want to adhere to a common practice in several Z80 systems, where the memory space is divided in slots of 16Kbyte. To make this not too complicated, only 2 of these 16Kbyte slots can be mapped to another 64k memory bank.

So, the Kernel_slot1 mode allows you to map any of the 32 blocks of 16kByte into slot 1 . Eight banks of 64K can be chosen with the blue BS signals, while within such a 64K bank, a 16K block can be chosen with the orange BLK signals. Slot0, 2 and 3 will select the 64K bank that is defined in the microcode instruction (with the yellow BNK signals).

The Kernel_slot3 mode allows you to map another block in slot3. But this has a few restrictions. The mapped-in block can be any 64K bank, but within that bank it is always block3. And no code can be executed from the mapped-in block.

In the table, the bits indicated in RED show which bits are needed to select a certain mode. For the bank select register, there are only 3 types: Application/Native, Kernel_slot1 and Kernel_slot3.

VIDEO CHANGE

In the current video system, in the 640-pixel mode, a byte from memory represents 8 pixels, and the byte tells for each pixel if it has foreground color or background color.

But this system was designed when the processor/memory cycle was still 160nS.

Now that I changed the cycle time to 80 nS some time ago, a fetched byte only needs to provide color for two pixels (pixels last 40nS). So we can simply have 4 bits (16 colors) per pixel ! Now each pixel can have an independent color. This seems much more flexible than the previous system, so I'm gonna change that.

VGA connector footprint issue

It turnes out that all KiCad footprints for these DSUB-15HD connectors are wrong, and that was known already 5 years ago, see this issue report. Swiching to the newest 8.0 version still had the wrong footprint. So I had to edit the footprint myself.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.