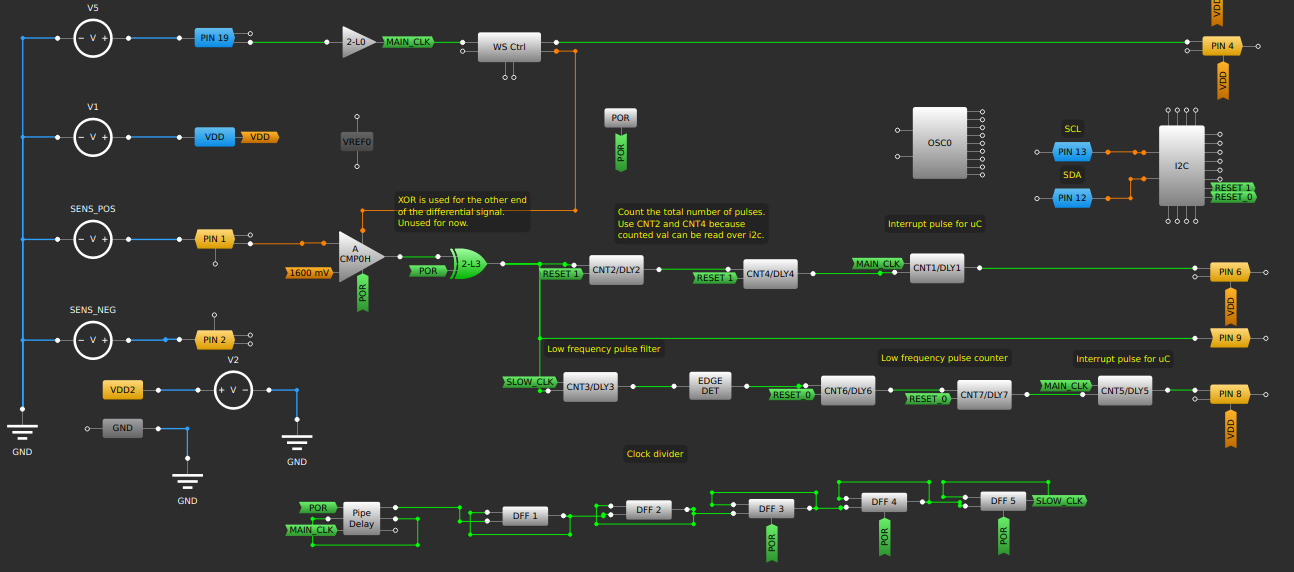

The most interesting aspect of YDrip is likely its programmable logic. This is where a lot of the heavy lifting happens, including tasks such as leak detection and revolution counting. While it's possible to use a low-power microcontroller as an alternative, the drawback is that it would significantly increase power consumption. This isn't ideal for a product designed to remain operational over many months. Some microcontrollers, like Atmel and TI's MSP, come with customizable hardware blocks capable of performing basic functions like hardware-based counting. However, their capabilities are somewhat limited. This is why I ultimately decided to opt for a complete hardware solution.

My initial approach was to use discrete logic chips until I found the GreenPAK product line from Renesas. Specifically, the SLG46826 model. It's reconfigurable, energy-efficient, and cost-effective ($1.60 for individual units). The package includes features such as analog comparators, counters, logic gates, oscillators, and more.

Analog to Digital

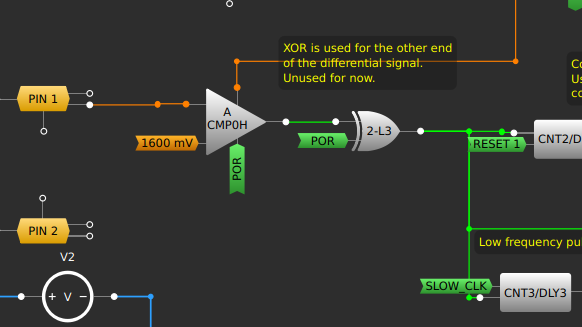

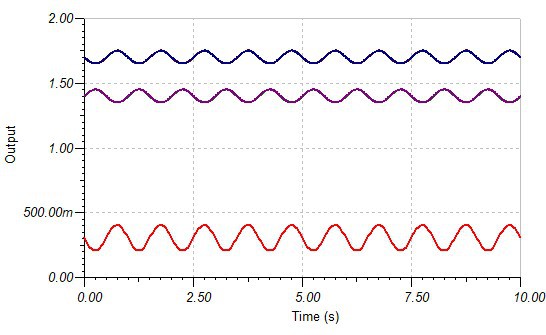

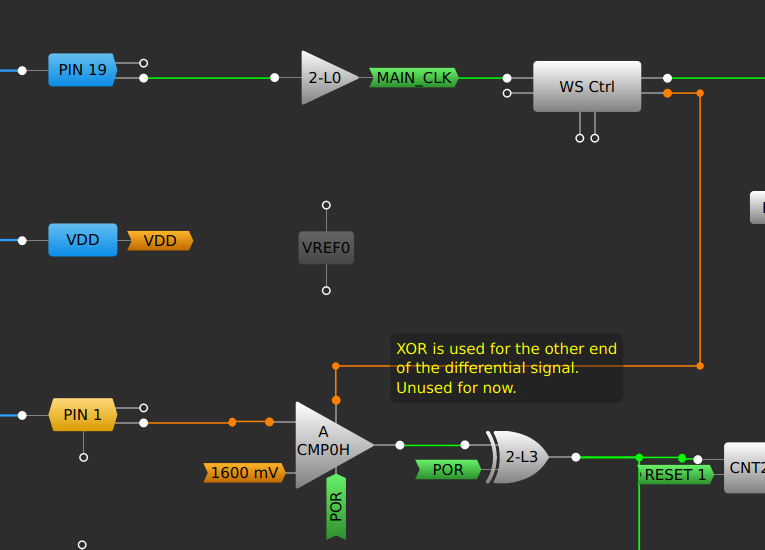

Starting from the left, the sine wave from the TMR sensor is fed into one input of the analog comparator. The other input is a reference voltage of 1600mV, which is the midpoint of the signal. Any voltage from 32mV to 2V can be selected in increments of 32mV. In earlier designs I used two comparators. One for each differential output of the TMR sensor and XOR'd them together. This provided no benefit so I removed the second one. Using a differential signal would help if the difference between them was amplified, but I was not doing that at this point. Here is an example of a differential signal:

The red signal is the difference between the two signals above it and is twice as large. This improves the signal to noise ration and shows why differential outputs are used.

Pulse Counting and Leak Detection

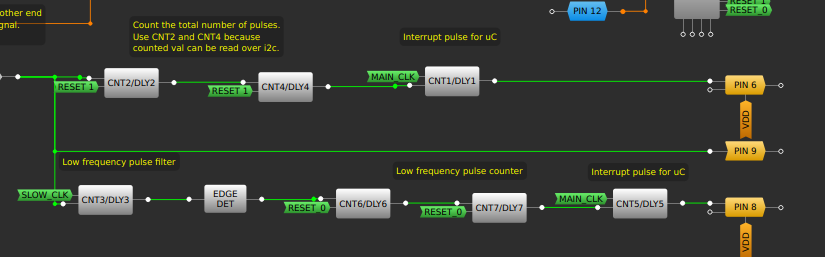

The high/low output of the comparator splits into two paths. The top path measures the total water usage. It consists of two programmable 8 bit counters. When they overflow that triggers a third counter configured as a one shot counter to send a short wake-up pulse to the ESP32S3.

The high/low output of the comparator splits into two paths. The top path measures the total water usage. It consists of two programmable 8 bit counters. When they overflow that triggers a third counter configured as a one shot counter to send a short wake-up pulse to the ESP32S3.The bottom path is the small leak detection logic. It low pass filters and counts the pulses. This filter is configurable via I2C. That value gets stored in two 8 bit counters and another one shot counter is used to send a leak interrupt signal.

Wake-Sleep Controller

A critical part of achieving a long battery life is duty cycling the magnetic sensor. It draws about 300uA. The wake-sleep controller can duty cycle power to the sensor and have the analog comparator only sample during 'on' times. This brings the system power down to only 55uA! See the previous post about power consumption. The main clock for the system is brought in from an external 32kHz RTC because the internal low power 2kHz oscillator is a little too slow.

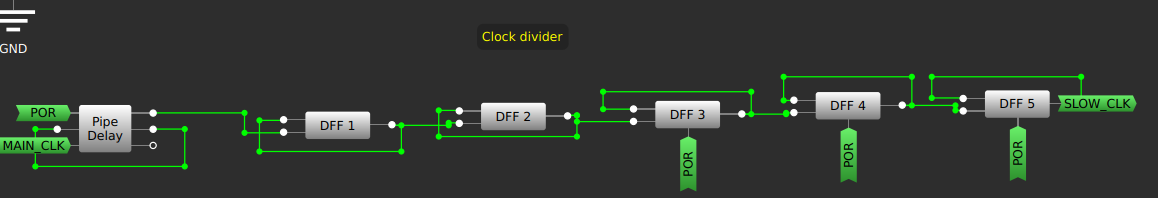

Clock Divider

Finally, a series of flip flops are used to divide down the 32khz clock to 64Hz. This slow clock is used to detect long running leaks by the low pass pulse filter.

Conclusions

By utilizing a mixed signal programmable logic IC this design was able to achieve a standby current of 55uA while also maintaining a variable wake-up time and leak threshold. Almost all of the logic blocks have been utilized in the SLG46826 making maximum use of it's capabilities.

ydrip

ydrip

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.