Initially efabless motherboard had this blinking program flashed into memory:

https://github.com/efabless/caravel_board/blob/main/firmware/gf180/blink/blink.c

In order to clean the flash we need to use option 6 from caravel_hkdebug.py:

> python3.8 caravel_hkdebug.py

Success: Found one matching FTDI device at ftdi://ftdi:232h:1:52/1

Caravel data:

mfg = 0456

product = 20

project ID = 0c002c69

project ID = 4b1a0018

-----------------------------------

Select option:

(1) read CARAVEL registers

(2) read CARAVEL project ID

(3) reset CARAVEL

(4) reset Flash

(5) read Flash JEDEC codes

(6) start flash erase

(7) check flash status

(8) engage DLL

(9) read DLL trim

(10) disengage DLL

(11) DCO mode

(12) full trim

(13) zero trim

(14) set register value

(q) quit

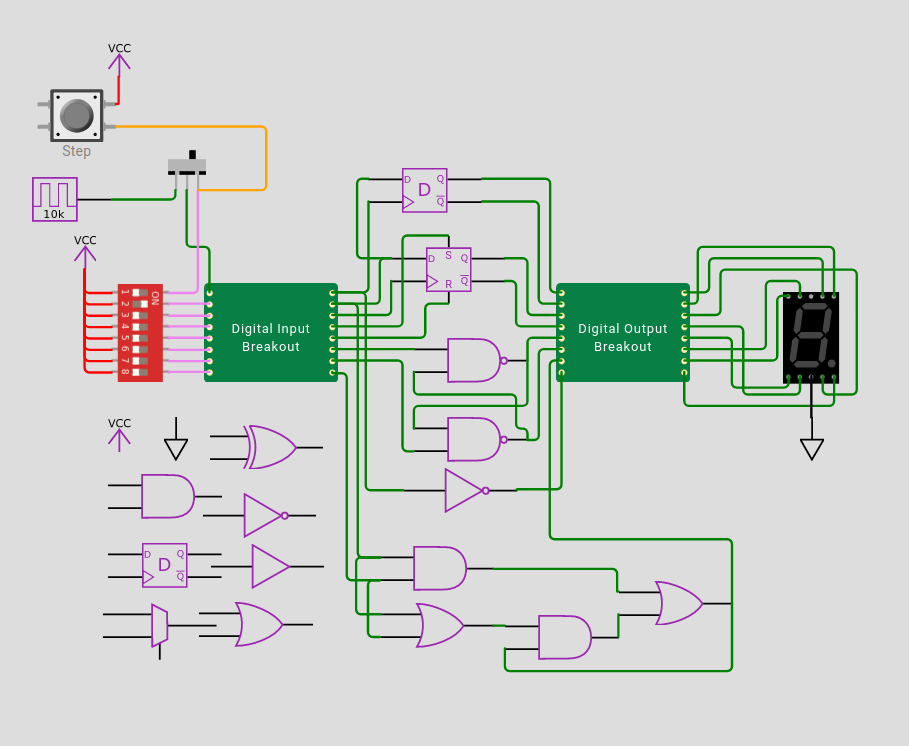

then chip is switched to user defined logic - in my case it was this simple test circuit:

This circuit was prepared with Wokwi online schematic editor and simulator:

https://wokwi.com/projects/348540666182107731

You can check Verilog output of this circuit using this Wokwi API URL:

https://wokwi.com/api/projects/348540666182107731/verilog

This Verilog was used for manufacturing of my version of the Caravel chips:

https://github.com/shaos/tiny_silicon_1

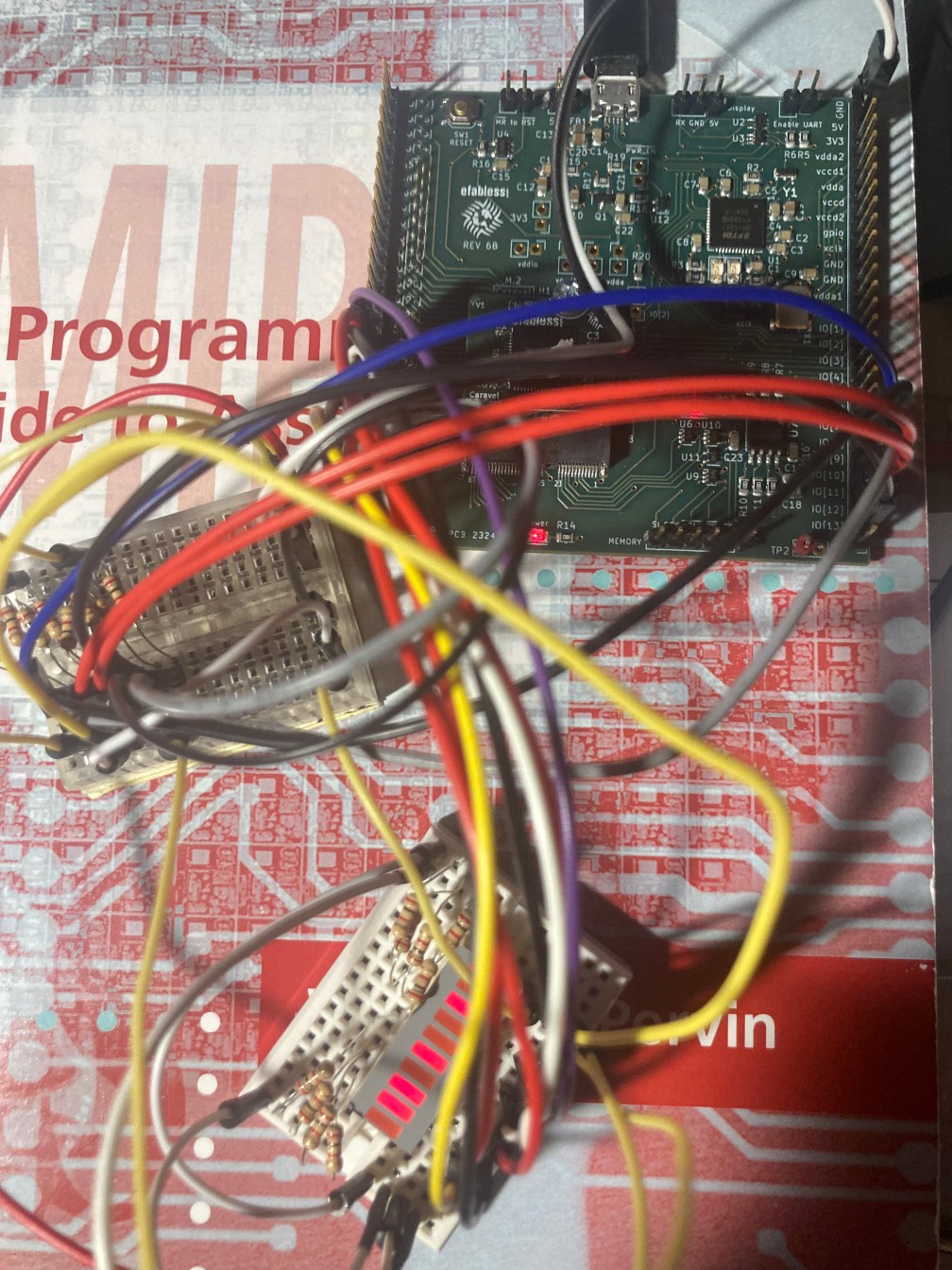

Apparently everything was working as expected:

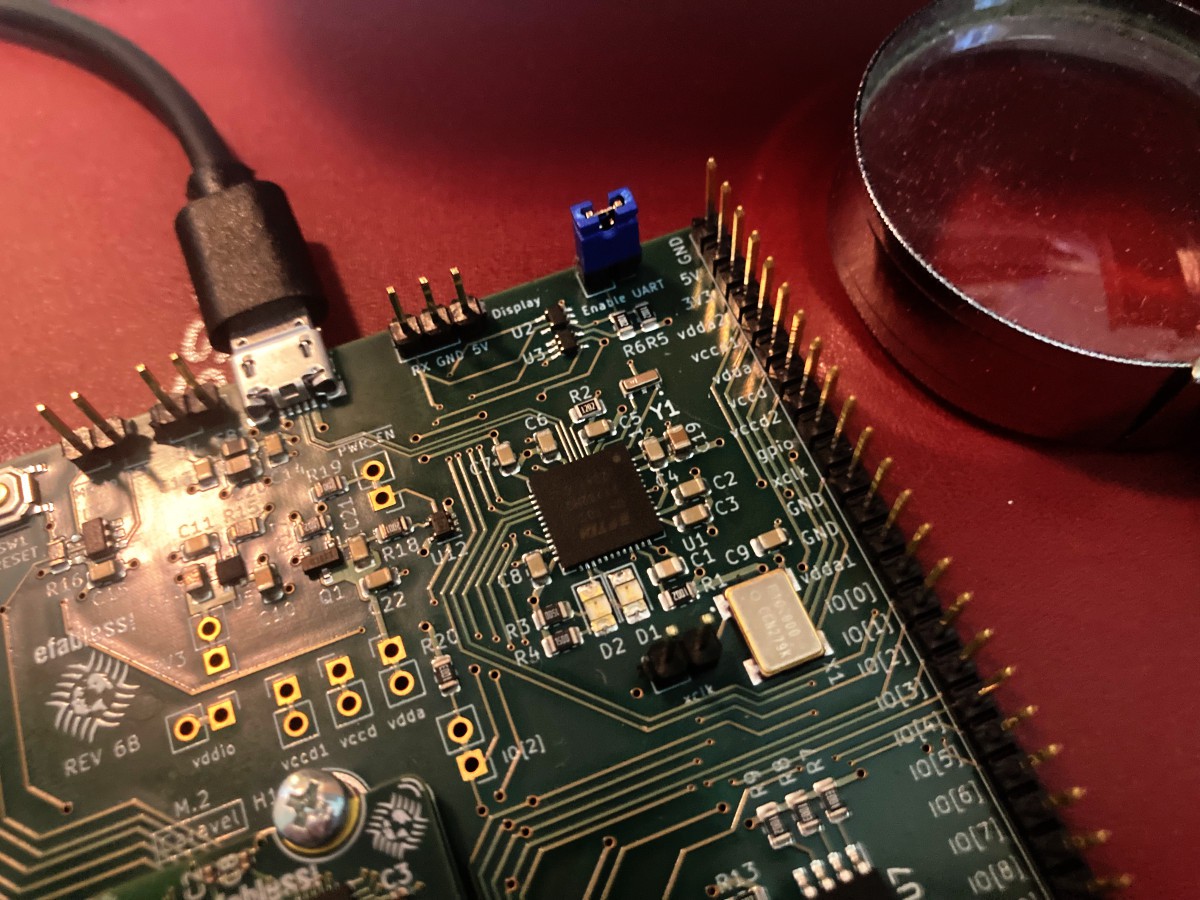

but better to use Caravel chip itself to test the logic - in this case we need to write a program that will produce some inputs, read some outputs and print some logs - Motherboard+Caravel is able to use serial communication with PC on speed 9600 that is enabled when this jumper switch in installed:

and we need to remove the jumper to flash SPI memory because both serial connection and flashing use the same FTDI chip.

Next project log will describe special program to test the logic from the chip itself...

SHAOS

SHAOS

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.