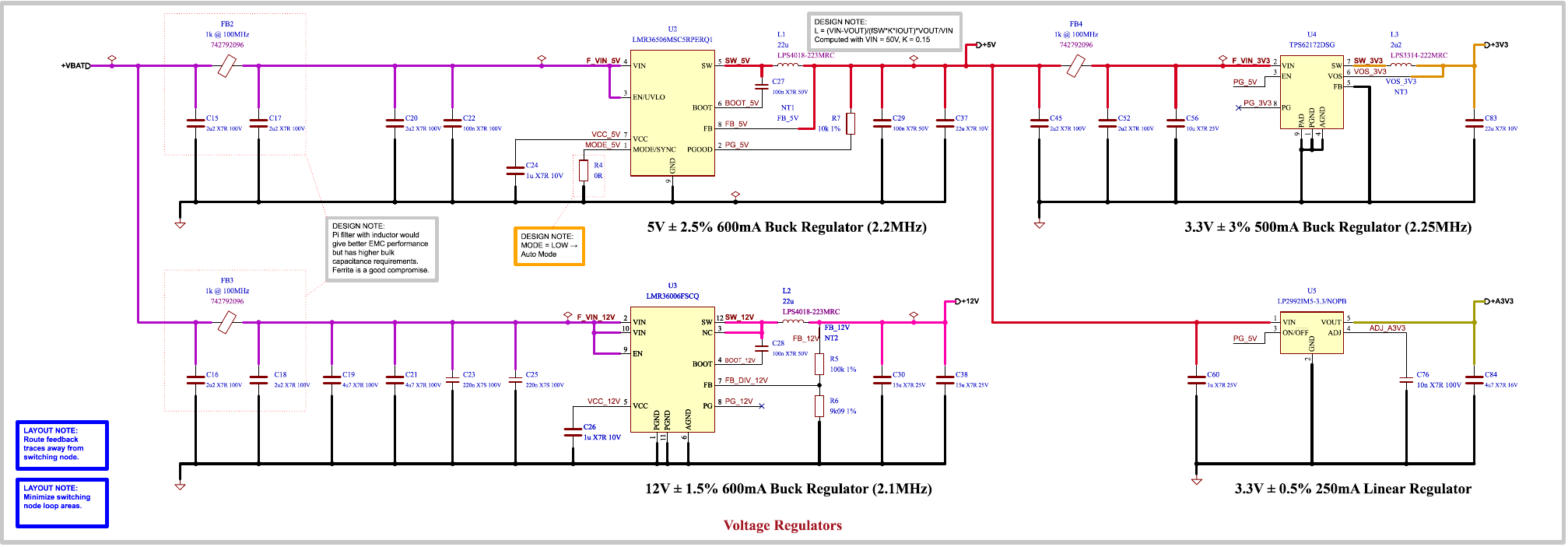

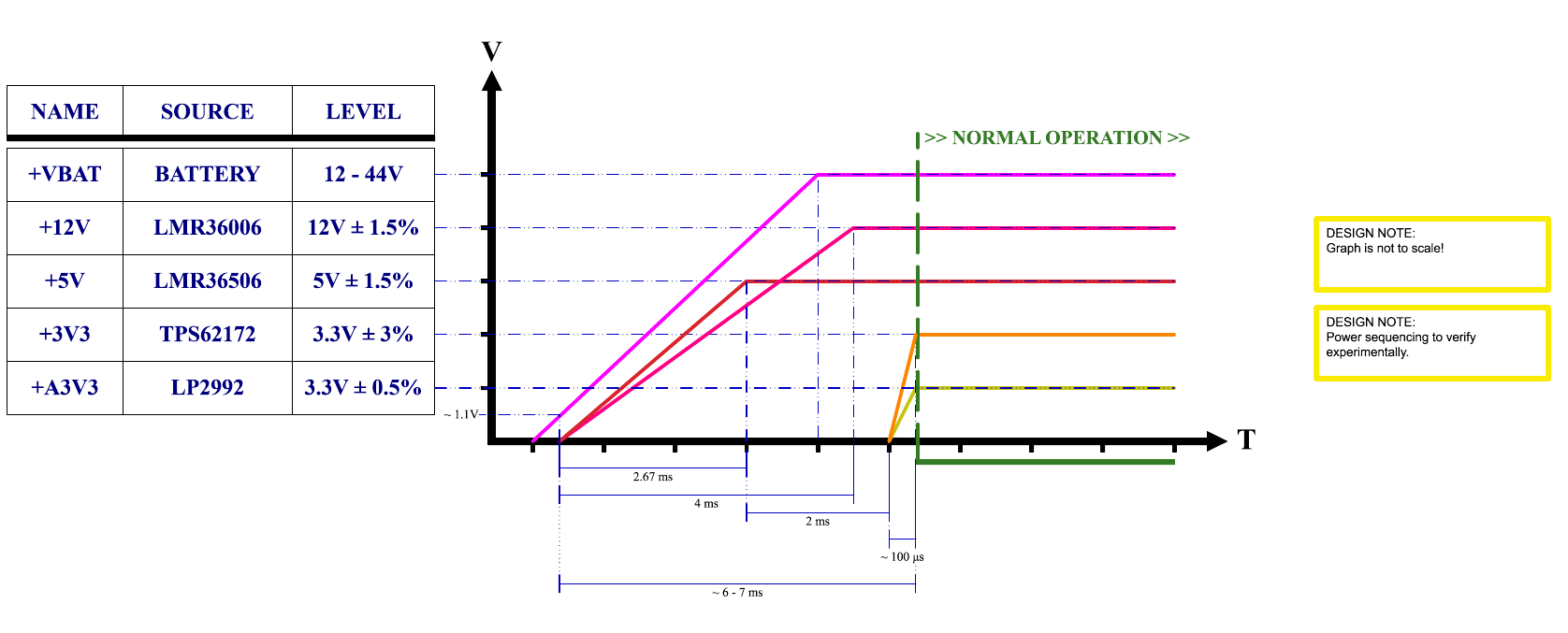

A power sequencing scheme was designed to ensure deterministic behavior on power-up. The regulators are sequenced as follows:

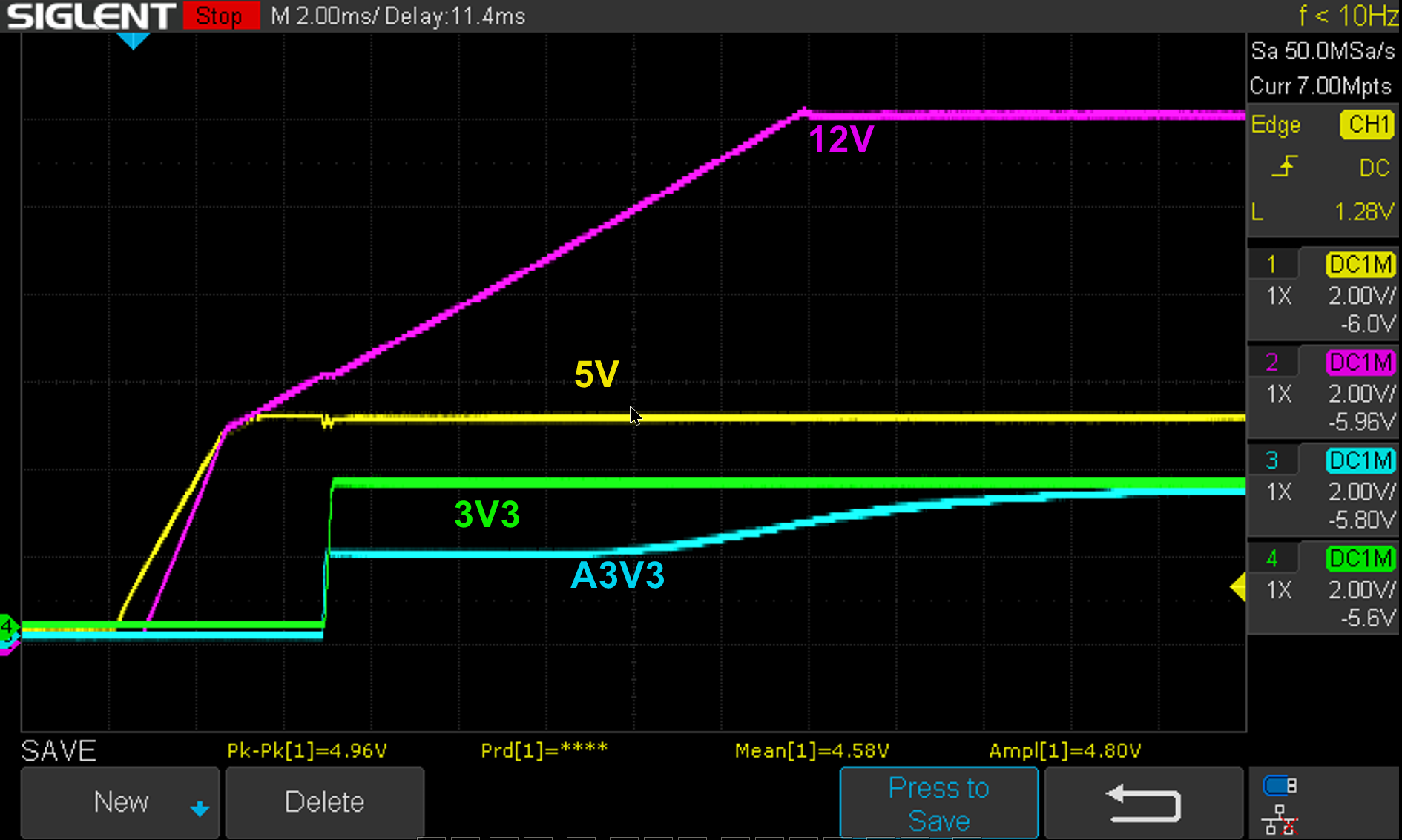

It is important to validate the power sequencing experimentally, to estimate the time needed for the board to be in a working state. The scoped signals are as follows:

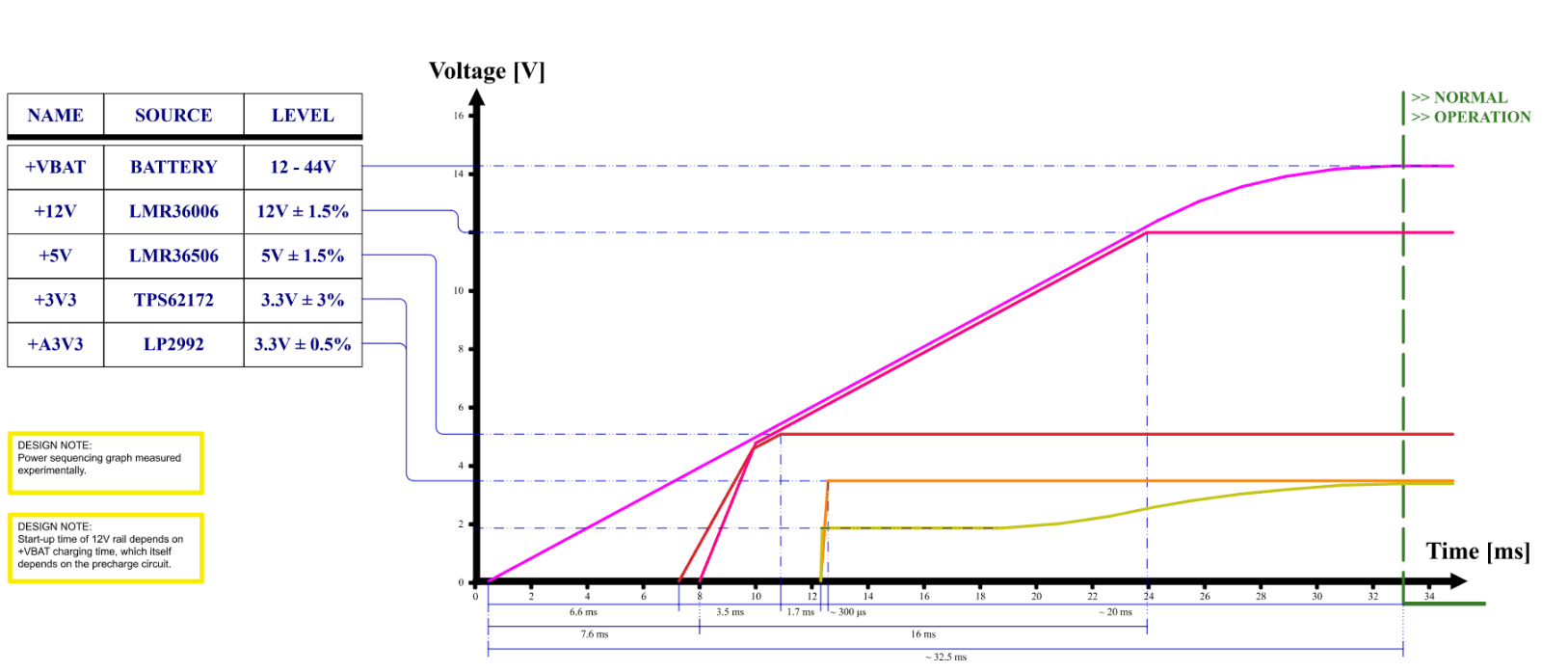

It can be seen that the power sequencing does not exactly follow the initial estimation. The most notable discrepancy is in the +A3V3 power rail (low-noise 3V3 rail), which has some sort of soft-start feature. This is an important feature to note, as the moteus firmware uses this rail as a reference for ADC measurements at boot-up, to determine board family and version.

The modified power sequencing graph is as follows:

Nguyen Vincent

Nguyen Vincent

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.