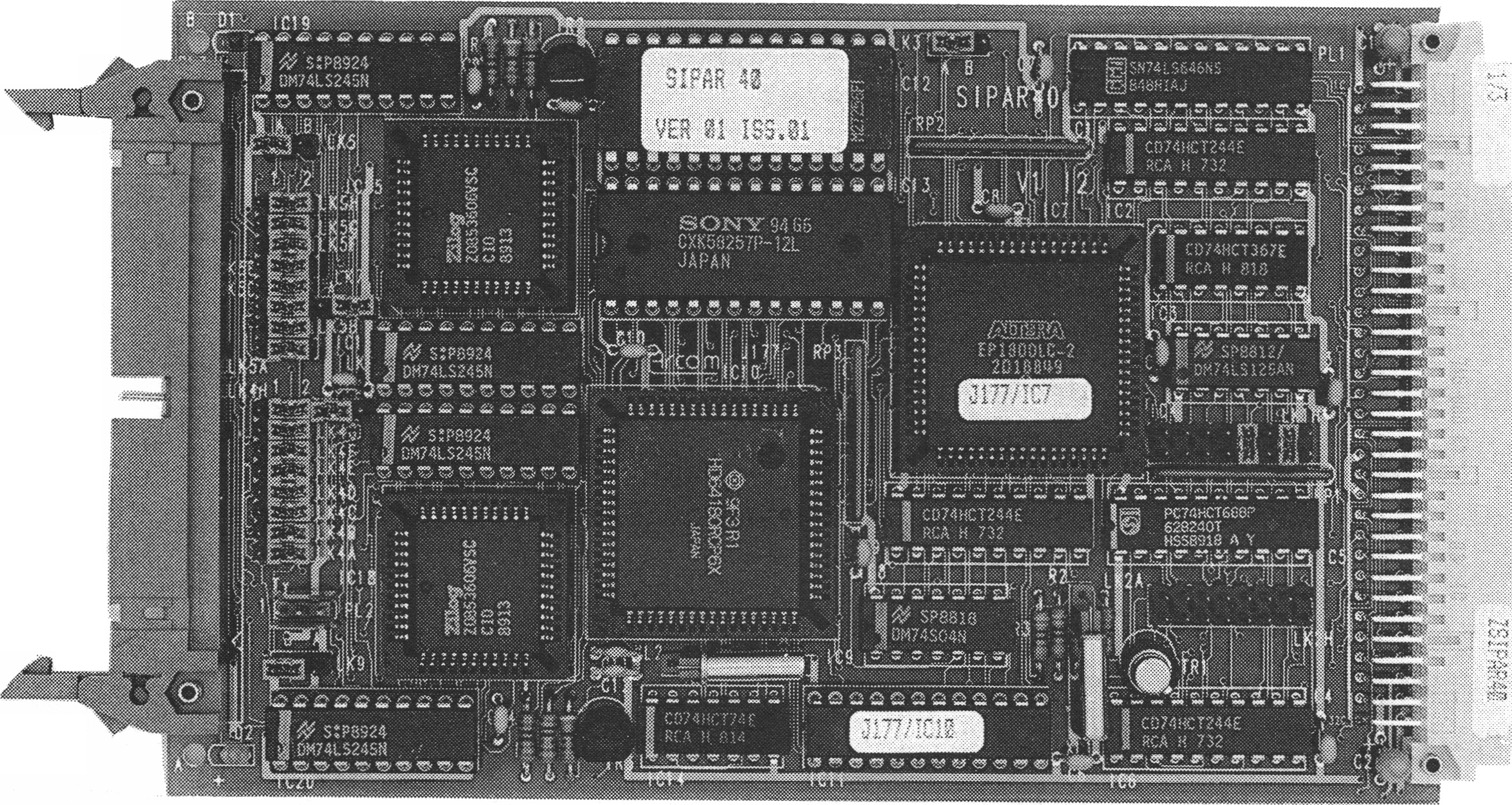

The SIPAR40 is an STEbus 40 channel parallel I/O board, with local intelligence in the form of a 64180 CPU running a high-level command language.

Two 8536 CIO devices provide standard parallel I/O functions plus multiple counter timers, change of state and interrupt inputs and pattern recognition. These resources can be configured for parallel I/O, frequency output or counting to 1MHz, and pulse/event totalisation. Sixteen of the board's 40 channels are fully buffered, 16 can be buffered for either input or output, and 8 are un-buffered. Sixteen channels are fully bit-programmable. The CPU is backed by 32Kbytes onboard RAM, 8Kbytes of which is dual-ported to the STEbus.

The high-level command language greatly simplifies digital I/O programming. In addition to system-level commands, some 20 high-level statements simplify parallel I/O programming including: 'ASSIGN', 'DIG' and 'IN' which would set a channel up for digital input for instance, and 'SCAN', 'INTERVAL', 'TOTAL' which simplify monitoring of I/O channels and events.

Interface:

STEbus slave interface.

Power consumption:

Typ 800mA @5V

Ordering Information:

SIPAR40: Intelligent parallel I/O board

Features:

- 40 parallel I/O channels

- CMOS 64180 CPU

- 32Kb RAM, 8Kb dual-ported to STEbus

- Counter timers

- Signal Conditioning Bus interface

Keith

Keith

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.