this is programming for a CPLD / FPGA the programming is the same but the pin planner is different

Schematic Version

VHDL version

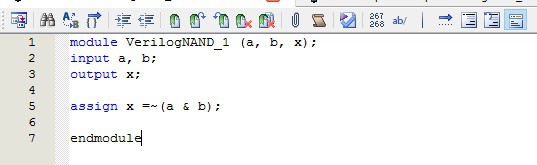

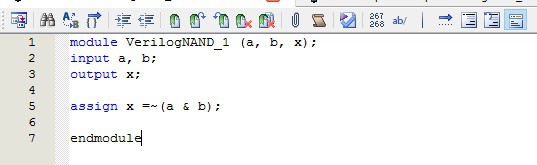

Verilog version

uploads the code to the CPLD/FPGA

A project log for Rosetta stone of hardware programming

Using Hardware and software to create the programming building blocks.

this is programming for a CPLD / FPGA the programming is the same but the pin planner is different

Schematic Version

VHDL version

Verilog version

uploads the code to the CPLD/FPGA

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.