My 512-bit Core Memory System

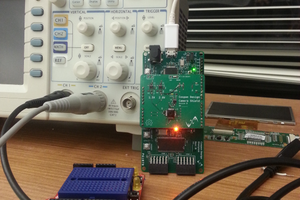

My memory is structured in 2 groups of 16x16 cores. The memory width is 2 bits, meaning 2 bits can be read or written at a time. By using several 4:16 decoders (constructed from 3:8 decoders), the desired location in the memory can be selected. Additional logic circuits were also used interface with the P and N Channel MOSFETS. Finally, a microcontroller (RP2040) was used to generate the waveforms to drive the memory and to perform tests.

Memory Tests

Several tests, including "GALPAT Test", "Half Select Current Switching Test", and "Image Writing and Reading Test" was run continuously. With a supply voltage of 3.20V, no error was detected within a period of 24 hours. This amounts to several gigabytes of data being read/written.

Dave

Dave

Bruce Land

Bruce Land

Erik Piehl

Erik Piehl

Pawel Jablonski

Pawel Jablonski