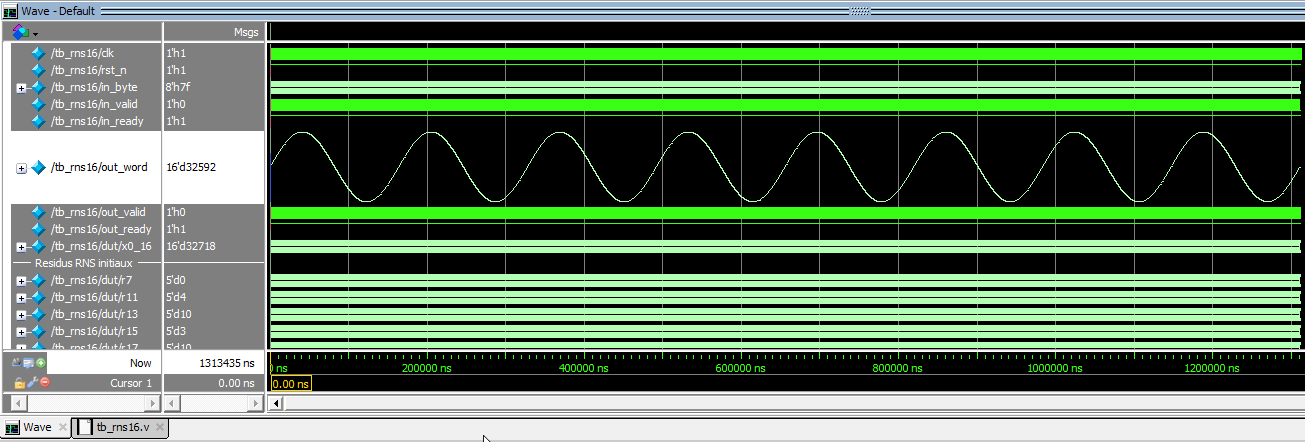

I’ve uploaded the new version of the RNS-based FIR filter, now extended to 64 TAPS (see PROGRAMME16BITS_FIRCOMPLET64TAPS.zip in project files) .

Everything is OK !

FIR Coefficients

The implemented coefficients are:

h_int = Columns 1 through 29 0 0 0 0 1 1 2 2 3 3 2 1 -1 -3 -6 -9 -11 -13 -14 -13 -9 -4 4 15 27 40 54 68 81 Columns 30 through 58 91 98 102 102 98 91 81 68 54 40 27 15 4 -4 -9 -13 -14 -13 -11 -9 -6 -3 -1 1 2 3 3 2 2 Columns 59 through 64 1 1 0 0 0 0

These coefficients come from a windowed sinc with a normalized cutoff frequency of 0.1.

They were scaled so that the sum of all taps equals 1024 (2¹⁰), allowing normalization after CRT reconstruction by a simple 10-bit right shift, with no hardware divider required.

All multiplication LUTs were completely rewritten to match these coefficients. The updated code is available in lut_verilog_64TAPS.v.

Implementation results

Target: Cyclone IV GX EP4CGX22BF14C6

Tool: Quartus Prime 22.1std.2 (Lite Edition)

| Metric | Value |

|---|---|

| Logic elements | 16 007 / 21 280 (75 %) |

| Registers | 7 982 |

| Embedded multipliers | 0 / 80 (0 %) |

| Memory bits | 0 / 774 144 (0 %) |

| PLLs | 0 / 3 (0 %) |

| Max frequency (Slow 1200 mV 85 °C) | 96.9 MHz |

This confirms that the 64-tap RNS FIR is entirely built from logic elements only, with no DSP usage : a fully LUT-based architecture.

Next step — Now that everything works:

Decouple the input data rate from the FPGA clock so that the 64-tap pipeline can handle inputs slower than clk without any data loss or misalignment, and simulate the full chain to verify correct behavior.

Then move on to the hardware implementation of the FIR.

Bertrand Selva

Bertrand Selva

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.