Development Roadmap

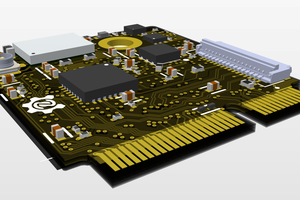

Phase 1: SPI Display Interface (Current) BeanBoard expansion PCB with 74HCT299 providing multiple hardware SPI interfaces, initially for the RA8875 TFT display controller. This enables text/graphics output on a colour display. The hardware SPI gives improved performance over a software (bit-banged) SPI implementation.

Phase 2: Cartridge Storage Removable EEPROM cartridge system for program and data storage, eliminating dependency on a USB host computer. Enables truly standalone operation - load from cartridge, save data / state to cartridge, swap programs without external tools.

Phase 3: System Redesign* Complete revision of BeanZee, BeanBoard, and SPI interface incorporating lessons learned. Unified design, optimized PCB layouts, and cyberdeck enclosure.

Core Components

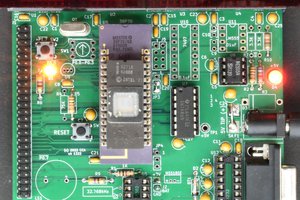

- BeanZee Z80 CPU board

- BeanBoard QWERTY keyboard

- BeanBoardSPI SPI interface board

- 800x480 TFT display with RA8875 controller

- Cartridge slots for removable EEPROM storage

- Integrated battery power supply and enclosure

Technical Details

At the heart of the system, the BeanZee CPU board has a 10MHz Z80, 32K ROM, 32K RAM and a UM245R USB module. There is an onboard monitor program (Marvin) which supports multiple consoles for input/output - e.g. USB and BeanBoard keyboard, LCD display and colour TFT display.

The BeanBoard keyboard implements an 8x8 matrix electronically - which is scanned directly by the Z80 - and is physically arranged as 16 columns by 4 rows, providing a sort-of traditional QWERTY layout. It also has a 20x4 character LCD display and includes an 8-bit GPIO for experimentation and interfacing.

The new hardware SPI interface uses a 74HCT299 universal shift register. This dedicated board eliminates GPIO bit-banging, improving performance, and was done specifically to make the TFT display more usable.

An Adafruit RA8875 TFT controller board is connected via the hardware SPI. This provides a 7.0" 800×480 pixel colour text and graphics display.

A cartridge system provides removable EEPROM storage, allowing multiple programs with data on removable media - a key feature making BeanDeck a proper self-contained computer rather than a development board. THis is not banked ROM, but rather programs and data are transferred to and from cartridge to RAM by the Marvin monitor.

Software Support

Marvin monitor provides a basic console, either over USB or the BeanBoard peripherals, and is able to load and execute programs, or inspect memory. It will be extended with RA8875 driver, EEPROM cartridge support, and extending console support to the TFT display.

Related Projects

Evolution from Z80 Breadboard Computer through BeanZee development board to complete standalone system

Sponsorship

This project is sponsored by https://www.pcbway.com/ who are providing PCB manufacturing for the BeanDeck system boards. I will use this opportunity to evaluate their services and appreciate the support they have offered.

Stephen Willcock

Stephen Willcock

Andrei V

Andrei V

Craig

Craig

David L Norris

David L Norris

twl

twl